Tool/software:

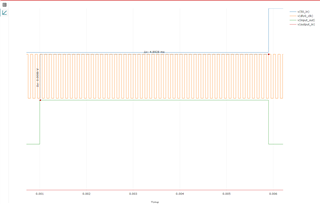

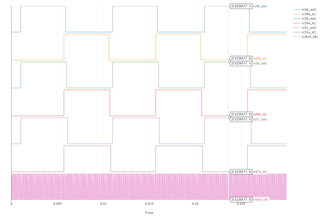

Pulse delay block are showing sensitivity to pulse duty cycle. I placed 3 delay blocks with a 47 count. The delay blocks are clocked at 10kHz. The top delay block receives a pulse with a 51% duty cycle at 10ms period.

The middle delay block receives a 50% duty cycle, and the bottom delay block receives a 49% duty cycle.

Only the middle delay block (with its 50% duty cycle) properly delays the pulse.

Chris Stell