Other Parts Discussed in Thread: SN74AUP1G14, TLV809E

Tool/software:

Hello,

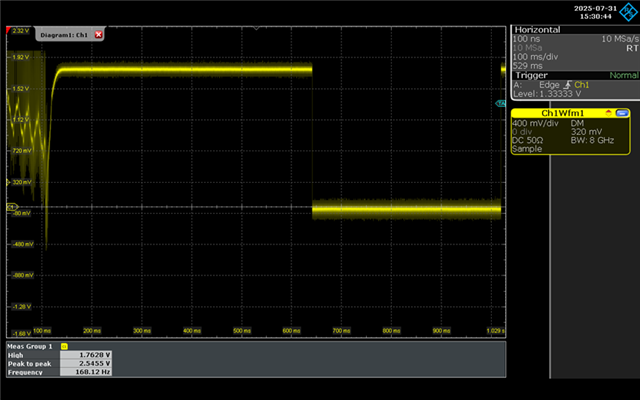

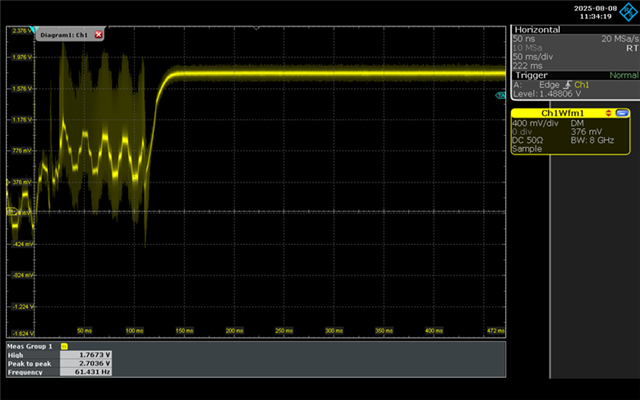

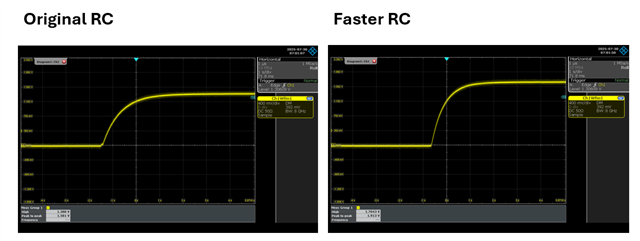

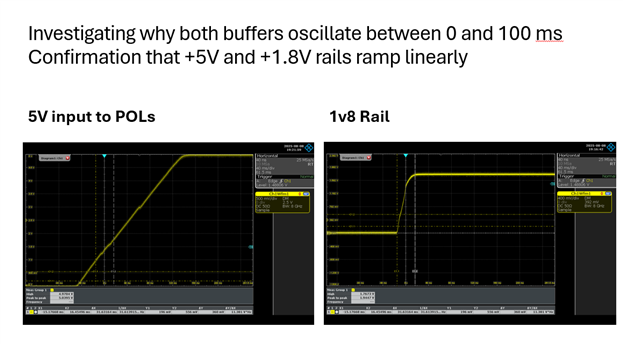

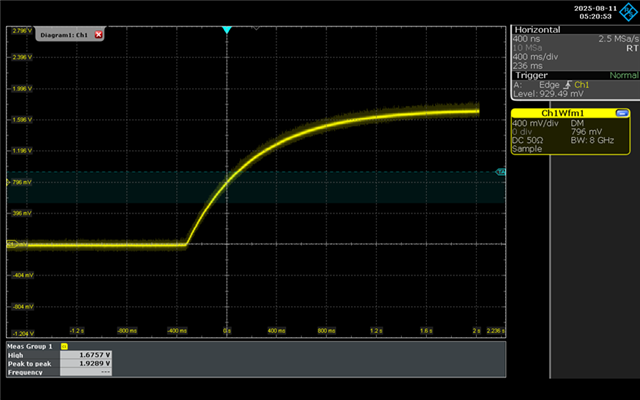

I wish to use a SN74AUC1G14 inverting buffer powered using 1V8: from the datasheet, VT+ is approx. 0.9V and VT- is approx. 0.5V respectively.

If I input a slow rising power-on-reset signal to SN74AUC1G14's input, can you confirm it will invert, i.e. output low, once the input exceeds approx. 0.9V.

If I input a slow rising power-on-reset signal to SN74AUC1G14's input, what will be its output state as the input rises from 0 to 0.5V and from 0.5V to approx. 0.9V?

My desired behaviour is for the output to go high at power-up and then go low after the rising input exceeds VT+!

Thank you