Part Number: TXS0102

Other Parts Discussed in Thread: TCA9416

Tool/software:

Hello,

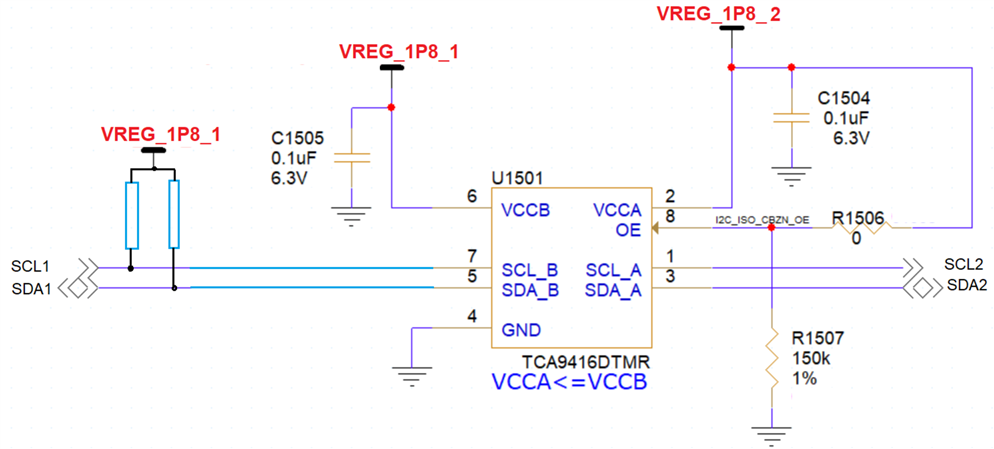

I am using the TXS0102 as a level translator between 1.8V and 3.3V for an I2C bus. There are external pull-up resistors configured as shown in the picture below. On the 1.8V side, I have 10 devices connected, whereas on the 3.3V side, there is only one device.

When I disable the TXS0102 by pulling the OE pin low, all 10 devices on the 1.8V side communicate properly. However, if I keep the TXS0102 enabled as shown below, the bus is pulled low and communication fails.

By removing the external pull-up resistors R1 and R2 on the 3.3V side, devices on both the 1.8V and 3.3V sides work properly. It seems that the sink capacity of the one-shot on TXS0102 is limited, which is causing the issue, although the datasheet does not provide any information about this. Could you explain the reason for this behavior?

Thanks,

Reza