Tool/software:

Hi Team,

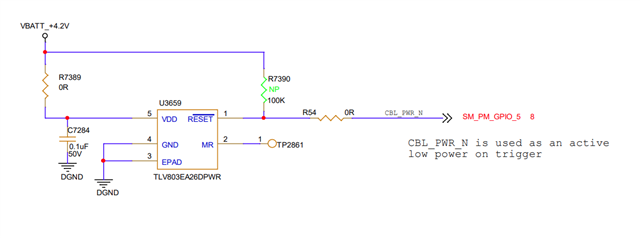

I'm using the part TLV803EA26DPWR in my design where one low pulse is required when VDD is supplied in a single power cycle.

My system needs a Low pulse as a trigger to boot up.

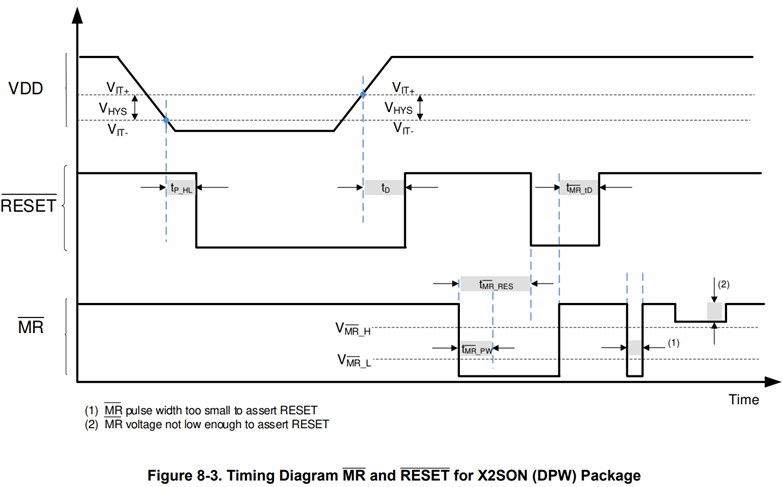

While supplying the VBATT_+4.2V, the system will encounter the following sequence,

1.VDD < VPOR - undefined state of RESETn

2.VPOR < VDD < VIT- RESETn will stable Low signal

3.VDD ≥ VIT- RESETn will stable Low signal

4.VDD ≥ VIT+ - RESETn will stable High signal

In the datasheet, the table 8-1 fourth row whether the VDD condition (VDD ≥ VIT–) is a typo?

Also let me know the understanding on the above sequence.