Tool/software:

Hello,

I encountered an odd behavior while using the watchdog time in a design through test on the EVM.

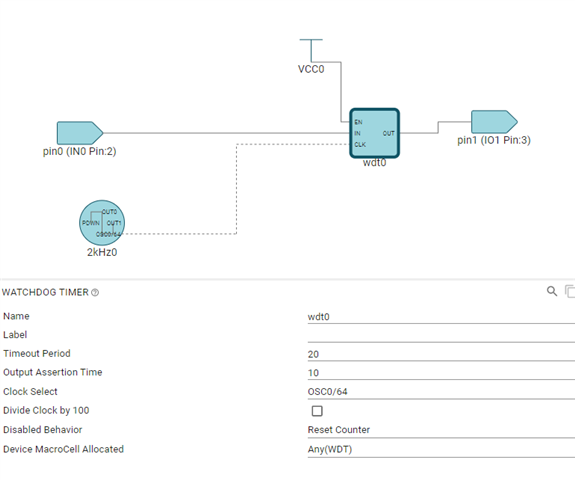

I had set the following:

- Clock select: OSC0/64

- Timeout period: 20

- Output assertion time: 10

I was expecting the watchdog fault to trigger 10ms after the refresh input stop to be toggled.

However, during our tests, the watchdog fault got triggered 15ms after the refresh input stop to be toggled.

It seems the fault is triggered after a delay equal to timeout period + output assertion time.

It's not a big issue for us, we changed the output assertion time as 1 cycle was fine enough but the behavior is either a bug or the description in the datasheet and ICS software has to be modified.

Best regards,

Clément