Part Number: CD74HCT4046A

Other Parts Discussed in Thread: CD4046B, SN74123

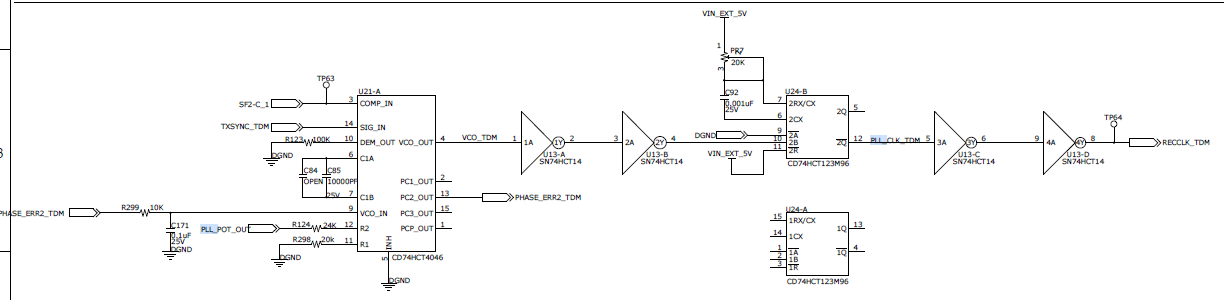

I have a PLL frequency setup using CD4046B where I generate 32 kHz from an 8 kHz reference

The feedback path divides the 32 kHz VCO output from which 32kHz 80% duty cycle clock is generated using SN74123 then from this clock, an 8KHz 25% feedback to pin 3 i generated using FPGA generated before feeding it back to the phase comparator (PC2).

The divider chain includes:

-

Schmitt trigger inverter

-

SN74123

-

Additional logic gates

With the CD4046B:

-

8 kHz reference input

-

32 kHz VCO output

-

PLL locks correctly

However, when I replace CD4046B with CD74HCT4046, the behavior changes:

-

With 8 kHz reference → PLL does NOT generate 32 kHz

-

With 4 kHz reference → PLL locks and generates 32 kHz

This suggests the effective feedback division may be behaving like ÷8 instead of ÷4 with the HCT version.

Questions:

-

Could the 74123 monostable in the feedback path be causing unintended extra division or edge distortion?

-

Are the TTL input thresholds of CD74HCT4046 affecting how feedback pulses are interpreted?

-

Does the PC2 comparator in CD4046B have internal multiplier?

Any insights into why the HCT version behaves differently would be appreciated.