Other Parts Discussed in Thread: SN74LV595A

I am using an SN74LV595A as an SPI output expander as many folks do. I would like to cascade two or more devices to allow for more than 8 output bits with a single SPI chain. There is a timing issue with doing this though.

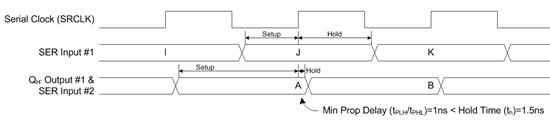

Common usage of an SPI port changes the serial data on the falling edge of the serial clock as would be appropriate to drive the SER input of the SN74LV595A as shown in the timing diagram on page 4. However, the timing of the serial output QH' changes state on the rising edge of SRCLK. This creates an issue with the hold time into a cascaded SN74LV595A. The datasheet gives the 3.3V required hold time as 1.5ns but the minimum propogation delay from SRCLK to QH' is 1ns.

Is there an easy way around this? Are there any similar parts to the SN74LV595A that update QH' on the falling edge of the clock?

Thanks.