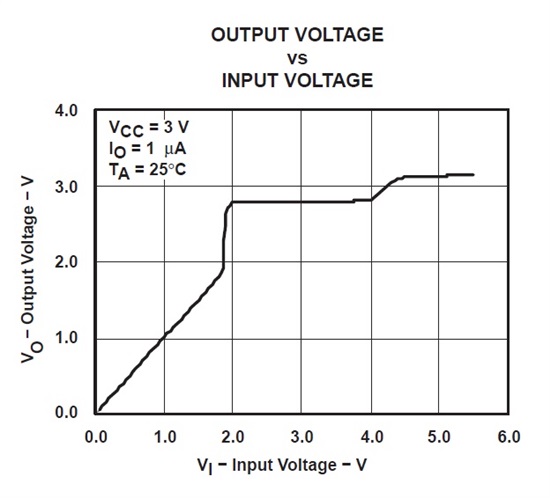

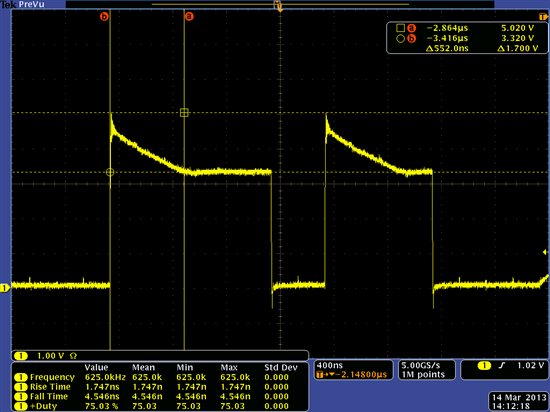

Does CB3T logic provided level translation in either direction? For example, for a CB3T device with VCC = 3.3V, would a 5V level input to Port A be clamped to 3.3V at Port B, and vice versa (Port B to Port A)? I'm using a SN74CB3T3384PW device and have a 2.5 MHz, 0-5V clock input to pin 2B1. The resulting output at pin 2A1, however, has an amplitude of about 4.6V ramping down to 4.0V. It's clearly not clamping to 3.3V. Any help with this would be greatly appreciated.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.