Other Parts Discussed in Thread: LSF0108

Hello,

I have one question with the LSF0108 level shifter..

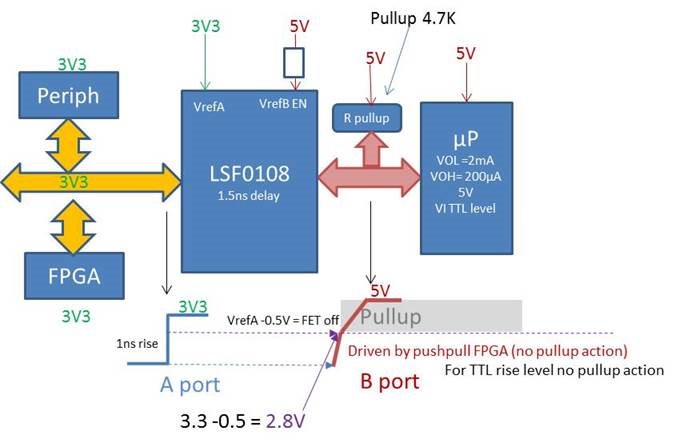

Here is the use case: FPGA/Periph <--> LSF0108 <--> uProcessor

The µP can drive only up to 2mA max at low level, I cannot use a low value of R for pullup on the B port of LSF0108.

The processor has a TTL level for inputs, and from DS the LSF0108 turns off the FET at 3.3V -0.5V =2.8V (Vref_A - 0.5V)

- It Means I have at TTL level 2V up to 2.7V driven by FPGA CMOS driver( Pushpull) and after 2.8V is pulled by the R pullup on B Port ?

- The range 0 to 2.7V is driven by CMOS and I have a fast time, and does it mean when the level is higher than 2.7V, the FET turns off and the port B is driven by the pullup ?

If the signals Rise time is 1ns at input of port A in range 0 to 2.7V, and the delay of LSF 1.5ns,

Is the output signal at port B transmitted and driven by CMOS FPGA, before the FET is off ?

If Yes, is it ok to use some Pullup of 4.7K ?

Thanks,

Mohamed