Hi,

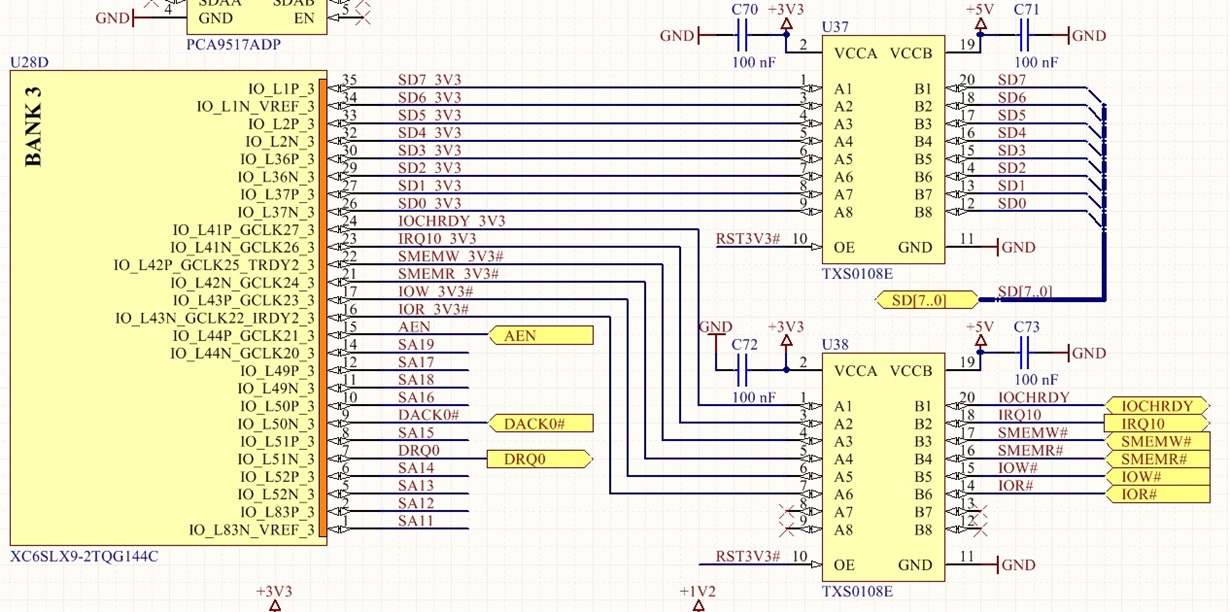

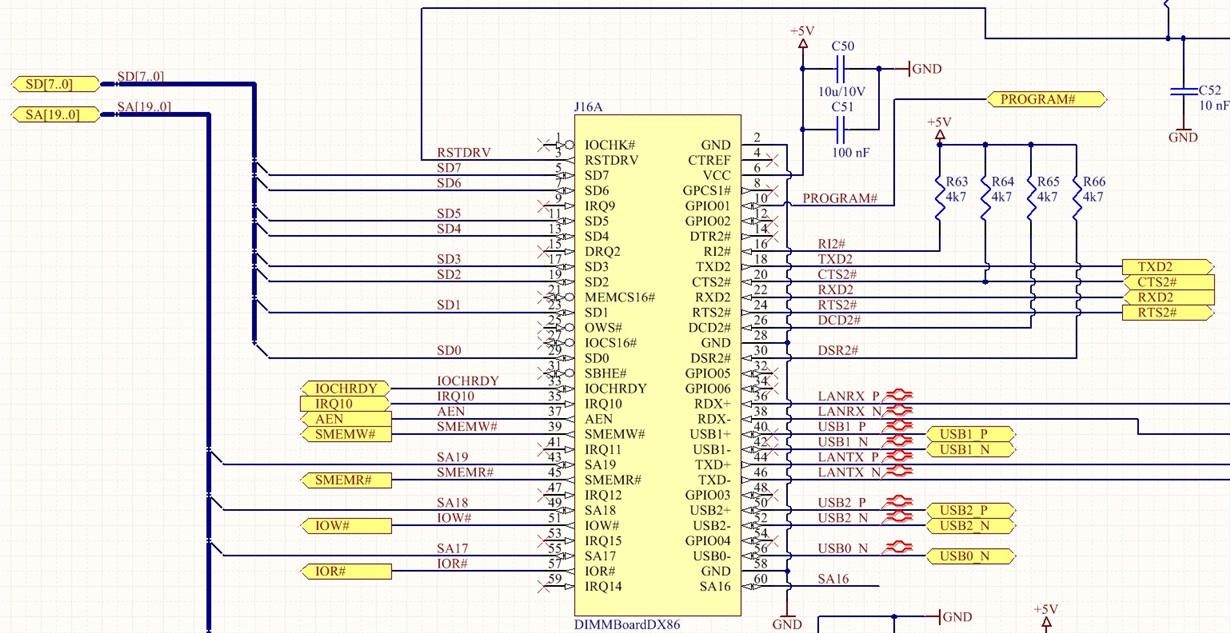

I use a TXS0108E voltage level converter between a Spartan 6 FPGA and a Vortex86DX based processor board. The processor board implements an ISA bus, that is connected to the FPGA. The FPGA is connected to the A side of the converter, Vcca is +3.3V. The processor's data bus is connected to the B side of the converter, Vccb is +5V. The processor data bus has 4.7k pullup to +5V on each data bus signal.

There is some problem when the processor reads the FPGA. It happens relative rarely, mostly after power up, and ceases after some time.

I made some oscilloscope screenshot. The processor reads 4 bytes from the FPGA's memory, and writes them back to another location, and so on.

The logic analyzer's D0:D7 channels show the data bus at the processor side. Channel 1 (yellow) shows the decoded read signal of the processor. Channel 2 (green) shows the decoded write signal of the processor. Channel 3 (blue) shows D0 data line on the processor side. Channel 4 (pink) shows D0 data line on the FPGA side.

The second screenshot is the same as the first, just a bit streched. On the first read cycle, the data on the FPGA side (pink) seems normal, but the level converted side (blue) shows a strange slow setup. The processor sometimes reads this bit as 1 instead of 0. It happens not only on D0, but on other data lines too, but I did not have enough channels on the oscilloscope to show more data lines.

So I wonder, what can cause this phenomenon. As during processor read, the TXS0108E drives the data lines, I presume that driver is the cause.

Best regards,

Laszlo Laczo