Other Parts Discussed in Thread: SN74LVC2G74

Hi Community,

I am using this d-type flipflop with ¬Q and D connected. Clock input is a debounced push button with really slow rising edge and falling edge. Both PRE and CLR are pulled on high. So my flipflop converts the button into a switch.

Can someone clarify what "Clock triggering occurs at a voltage level and is not related directly to the rise time of the clock pulse" (see SN74LVC2G74 Datasheet on page 1 "DESCRIPTION/ORDERING INFORMATION") really means?

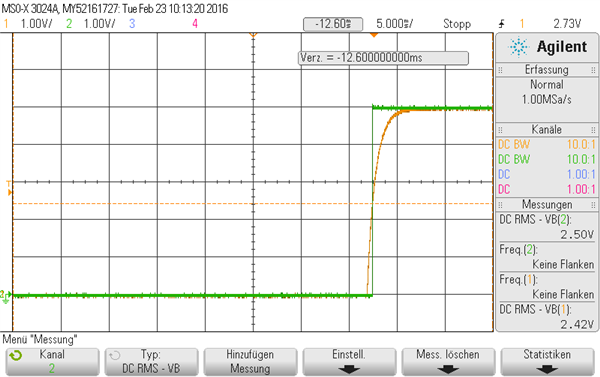

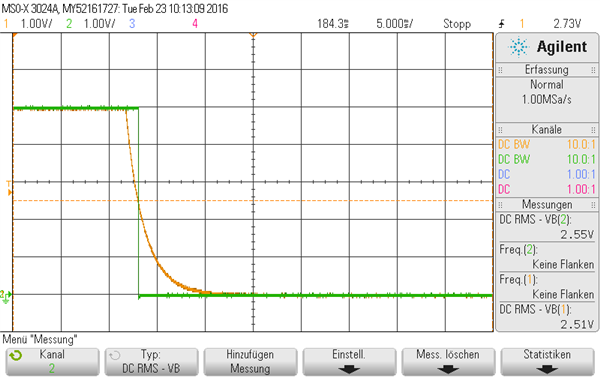

Right now my Q follows the operation of the pushbutton but with harder edges (like a schmitt trigger without hysteresis). It triggers on both rising and falling clock edge. So if pushed Q is high and on release it's low.

I don't know why it's not working like expected. I thought it's positive edge triggered with no relation to my rise time, why is it changing Q to low on a falling clock edge?.

orange = debounced pushbutton on clock input

green = Q of Flipflop

Thanks,

Stoane