Hi,

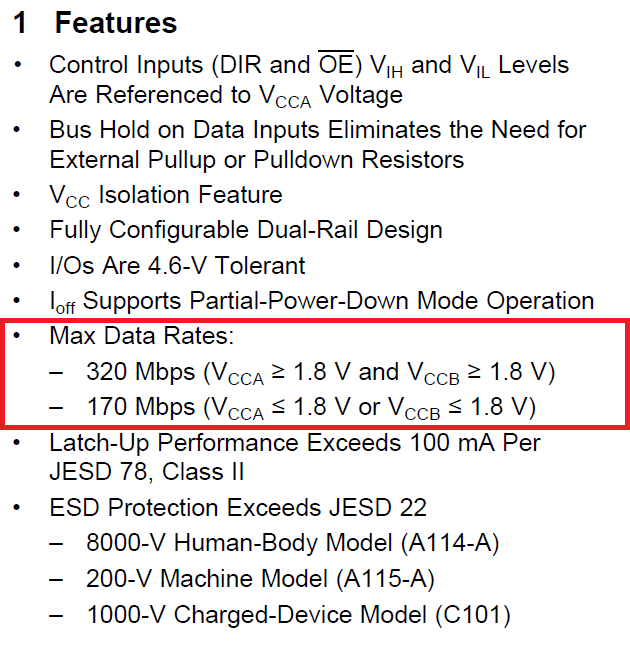

I calculated ICCB maximum for SN74AVCH8T245RHLR voltage level translator as per the following equation:

ICCB = static ICCB + dynamic ICCB

as per the following link

The maximum ICCB current as per my calculation was 92.4mA for 250MHz frequency.

The absolute maximum current through ICCB is 100mA.

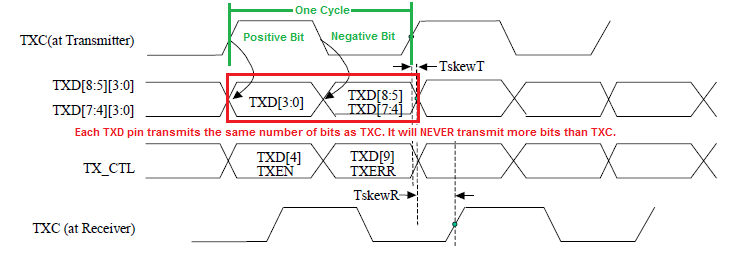

The frequency I have chosen is wrt RGMII LVCMOS interface.

Is there any problem , because the absolute maximum and calculated ICCB is really close?

Can I use SN74AVCH8T245RHLR for level translating RGMII signals?

Regards,

Bhavya