Dear Team,

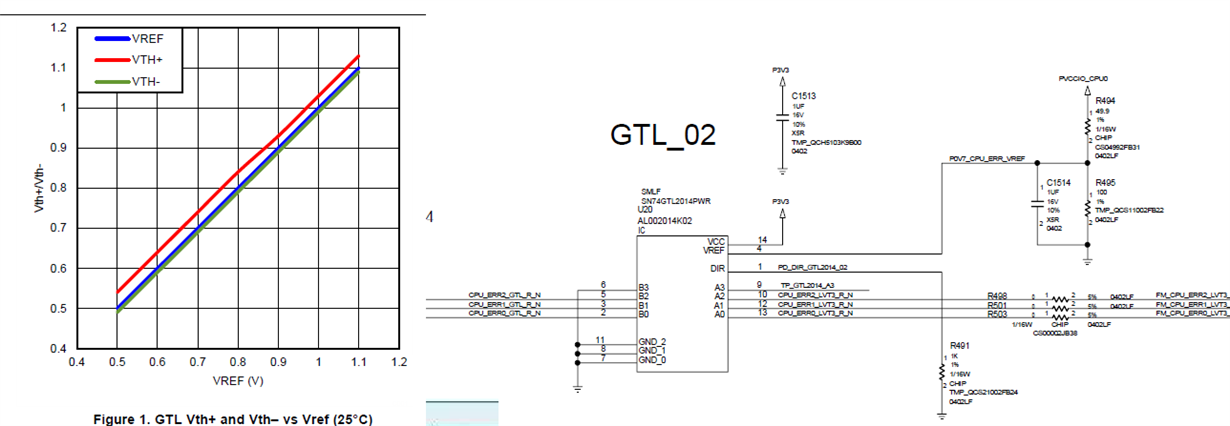

There is a design doubt about GTL2014. According to TI’s reference design, Vref is using PVCCIO which the PWR bring up after P3V3, thus we would like to change PWR doamin to P3V3 making GTL2014 operated at same time when P3V3 bring up, does TI identify this design?

Thanks!