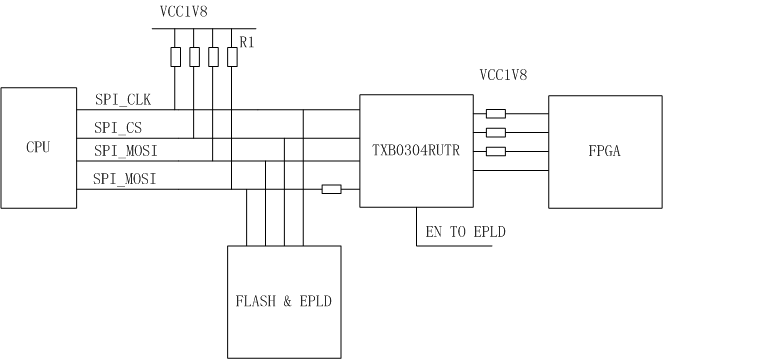

hi dear supporting team,

customer is using TXB0304 in below way, they are using it for isolate the connection with FPGA with enable function, to avoid when FPGA is not powering up, FPGA pull the SPI bus. both side are 1.8V level, according to our d/s,

1. output could not be pulled up, so they only use pull up at input, R1 want to be higher than 20k, others using 4.7K

2. When open oneshot, the MOS internal resistance is almost 0, they add serial resister at TX side.

could you help check whether it is ok or not for the design? tks a lot!