Other Parts Discussed in Thread: SN74LVC1G17, SN74LVC1G14

In almost any digital design, clocking or resetting a FF (Flip Flop) is almost ALWAYS decided by some logic conditions. For example: a counter must be reset when, say, A=47, and B is true and C is false, OR D is less than 100 and .... etc. In any application, the moment to reset a FF is always determined by some combinational conditions decoded by gates.

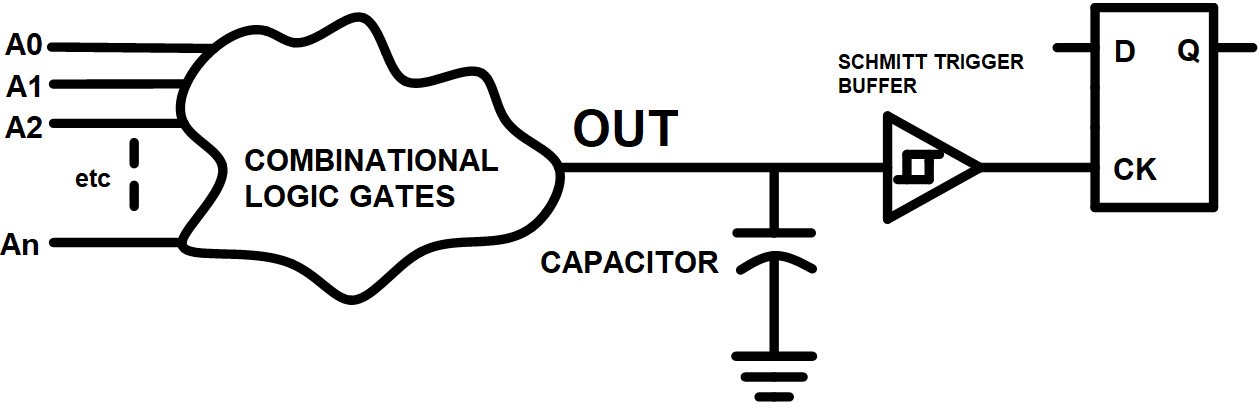

BUT: the output of any set of gates decoding some conditions (like the ones above) may be glitched, may have spurious undesired responses, due to gate delays.

My question is:

3- How does TI reset a 74HC74 Flip Flop (or an equivalent D FF) according to some conditions like the ones stated above, knowing that decoding this condition with gates will generate glitches/spikes (at the output of the decoder) that could (and will) falsely reset the FF.

2- Similarly, in almost any digital design, clocking a FF (or a whole function like a counter) is determined by some logic conditions decoded by a set of gates. Remembering that decoding with gates could (and will) generate spurious responses and/or glitches, how is it possible to clock a 74HC74 FF from a decoding circuit that could (and will: Murphy's law really works!) be glitched?

If these two questions are not clear enough, please feel free to ask for more details.

Please, tell us the way TI suggests to reset (or clock) a 74HC74 Flip Flop (or equivalent) , in the context above .