Other Parts Discussed in Thread: SN74LVC1G17, , SN74LVC2G34

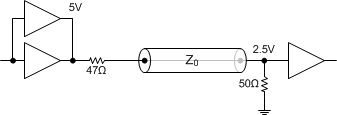

I'm trying to convert a 5 V clock signal running at 50 MHz down to a 3.3 V clock running at the same speed without inverting the clock. I was planning to use a buffer and have it be powered by a 3.3 V source, so when I buffer the 5 V clock, it appears as a 3.3 V clock signal. I started using the SN74LV1T126, and I took the PSPICE model from the product page, imported it into my simulator, LTSPICE, and ran a simulation. Without a load, inputting a 50 MHz clock signal produced a 3.3 V clock at the same frequency at the output. However, when a 50 Ohm load resistor is attached, the output was much smaller, around 1.86 V. I searched around for similar products to the SN74LV1T126, and I found that the SN74LVC1G17 is a similar buffer with a higher current output at 24 mA (at 3.3 V), and its timing characteristics are similar if not better than the SN74LV1T126. Timing is important since the clock signal is fast, so would the SN74LVC1G17 be suitable for my needs compared to the SN74LV1T126? I would have simulated it, but I found that there is no SPICE model for the SN74LVC1G17.