Hello,

I am using the D-FF with the specified part number in my application.

In order to check if the device is working properly (With lack of EVB) I soldered the device on a PCB I designed and started testing it with an advantest 93K testhead.

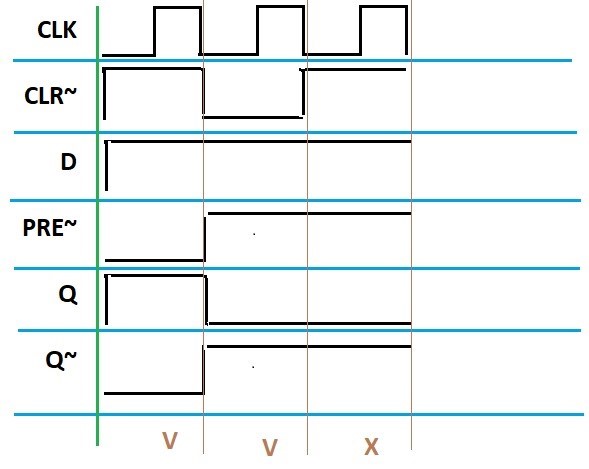

I started by validating Table 1. (Function Table) in the DS (Page 15) row by row and couldn't get it to work.

I started with PRE~ Low and CLR~ High so I got Q=H (As expected)

I then applied PRE~ High-Z and CLR~ Low and got Q=L (As expected).

I then applied PRE~ High, CLR~ High and a 1MHZ 50% D.C. Clock and started changing D (H - L - H - L) - Q isn't changing as expected.

Some devices didn't respond to both D-High and D-Low and some didn't respond to D-Low only.

I would like to know if there is a specific order for changing the D-Pin or if I have to do something in advance.

Thank you.