Hi Team,

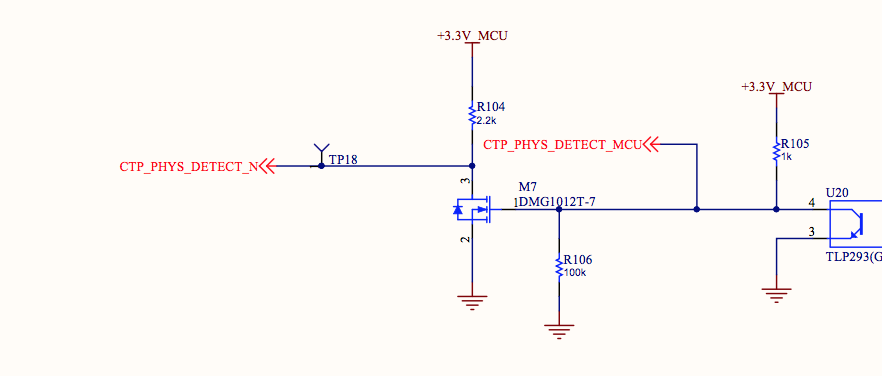

My customer is using the SN74AVC4T774 and are observing that one of the signal inputs on the B side (B2, pin 13) becomes shorted to GND internally in the IC. The B side is 3.3V side, and the A side is 1.8V. The 3.3V side is coming from a separate board (short cabled interface). GND is also passed over the cable. The signal is being pulled up to a different 3.3V power rail than the IC is on. Please see the attached schematic below for reference.

What might we be doing that could cause the chip to develop an internal short to GND? I am wondering if perhaps we are diode conducting on that pin, or if maybe the power sequence is wrong?

One thing to note is that the /OE pin is directly connected to the SoC (i.e. there is no pullup resistor), but we believe this probably doesn't justify the issue.

Any help or suggestions you can provide is greatly appreciated.

Thanks,

Mitchell