Part Number: SN74AUP1G17

Other Parts Discussed in Thread: SN74AUP1G74, TINA-TI, SN74LVC1G17, SN74LVC1G14, SN74AUC1G17

Hi Team,

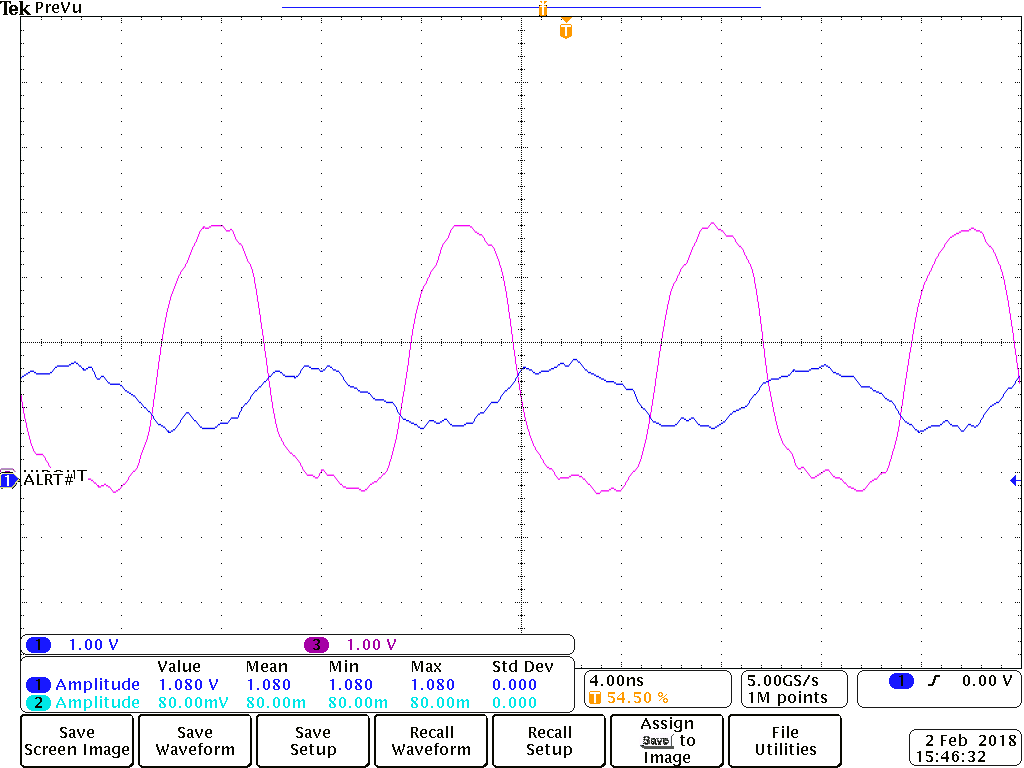

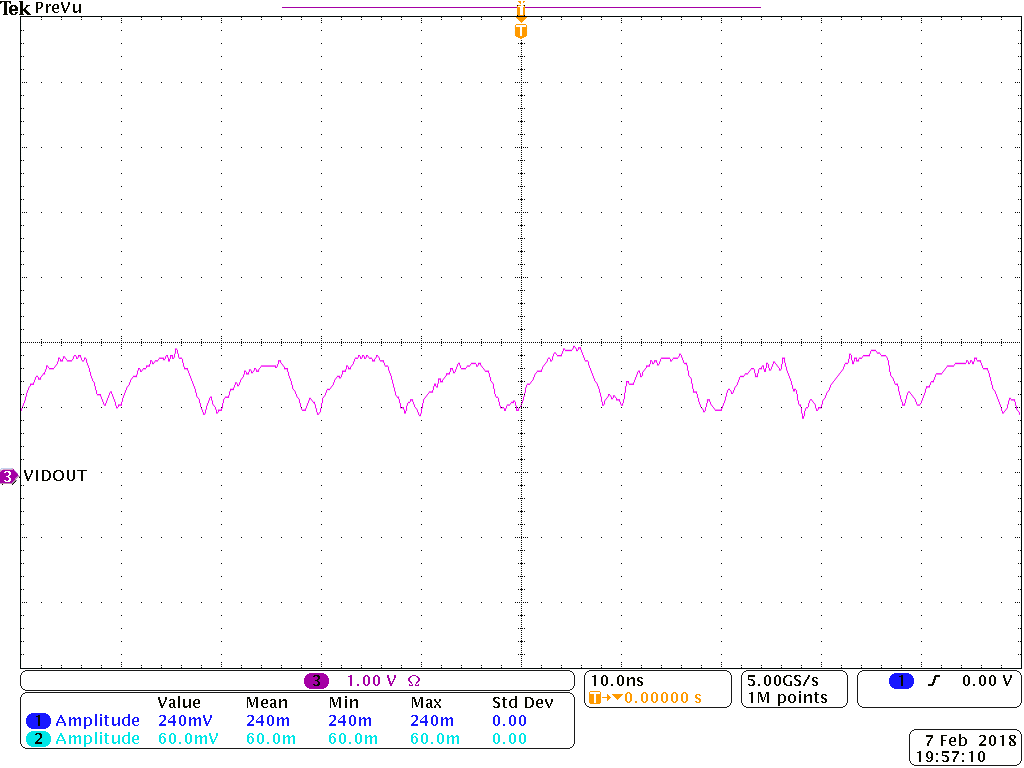

Is the SN74AUP1G17 capable of a 100MHz clock driven through it? What information in the datasheet can be used to determine frequency limitations if any? My customer is expecting to see a square waveform but instead it sounds like they are seeing a non-square waveform with dc offset attached to it. The device is operating at 1.8V. I have asked for a screenshot of the waveform, but wanted to get this question posted in the meantime.

If the SN74AUP1G17 is not capable of 100MHz, can you suggest a P2P device that is? The package is SC70.

Thanks,

Joe Stephan - FAE