Other Parts Discussed in Thread: SN74AVC4T774, LSF0102, TXB0108

Hi,

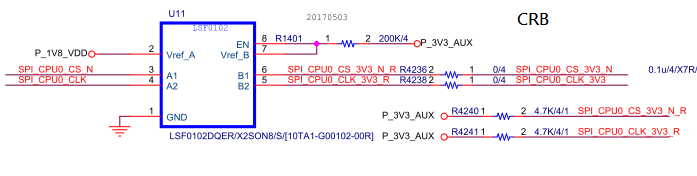

Customer is using LSF0108 for 8MHz SPI application from 1.8V to 3.3V with schematics below.

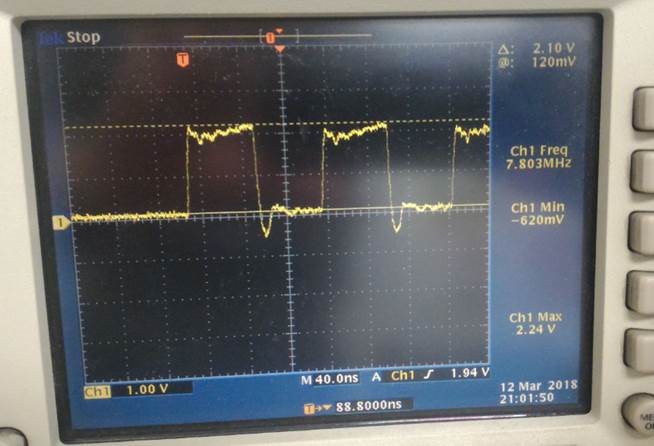

But, they found the output signal can't reach 3.3V and it seems to be a too slow rise time. The waveform as below is at output side (SPI clock) after they change output side pull-up resistor from 1Kohm to 200ohm. (With original 1kohm, the rise time is slower.) I think LSF0108 should be able to cover 8MHz of speed. What should they do to oversomce this issue?

Thanks!

Antony