Hi,

Need to know how to identify pin1 of the device. I am using SN74LVC2G125DCUR - VSSOP (8 pin package).

I see white line marking on one side whereas in the datasheet the index area is marked on one quadrant. Help me identify the pin1. Attaching image of layout for reference.

I need to have pin 1 near the white dot. Is this layout correct.

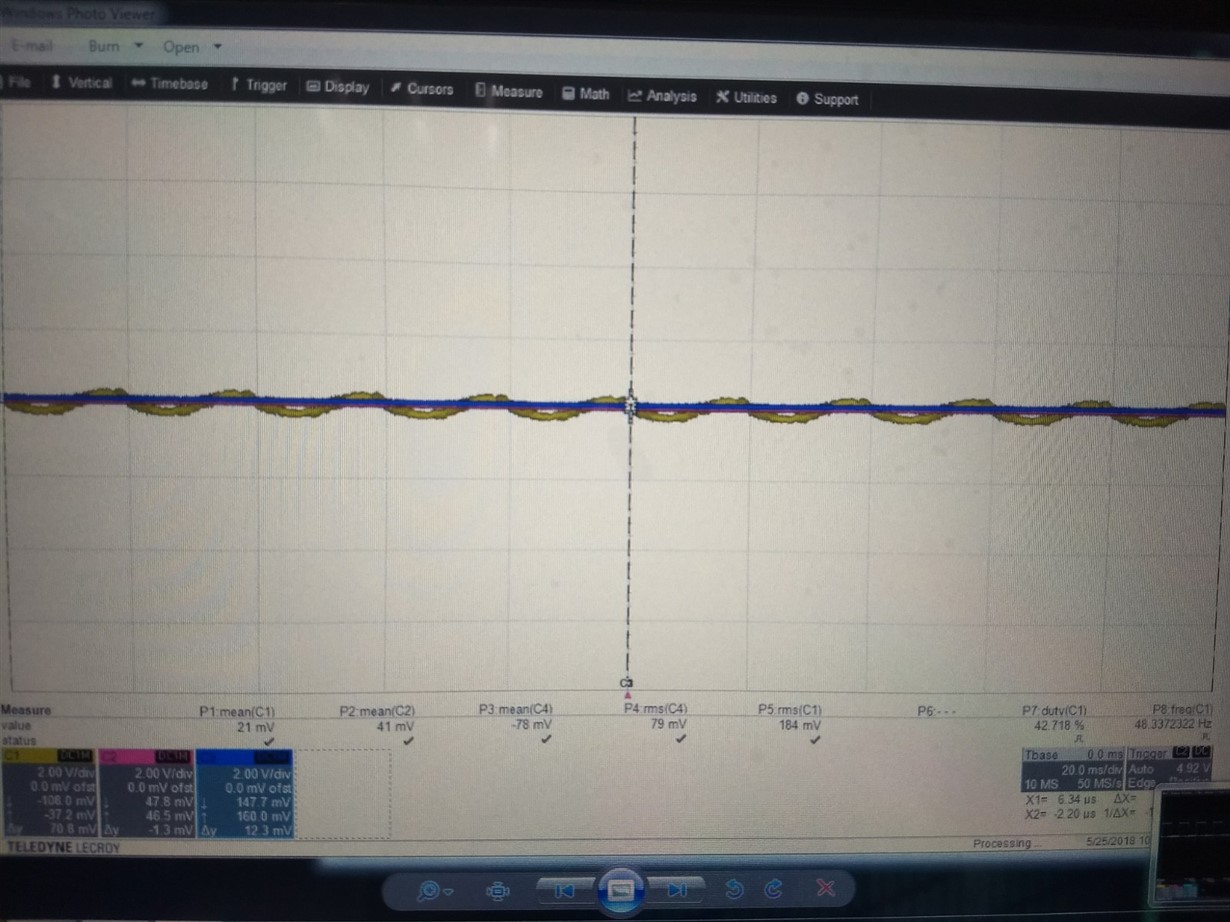

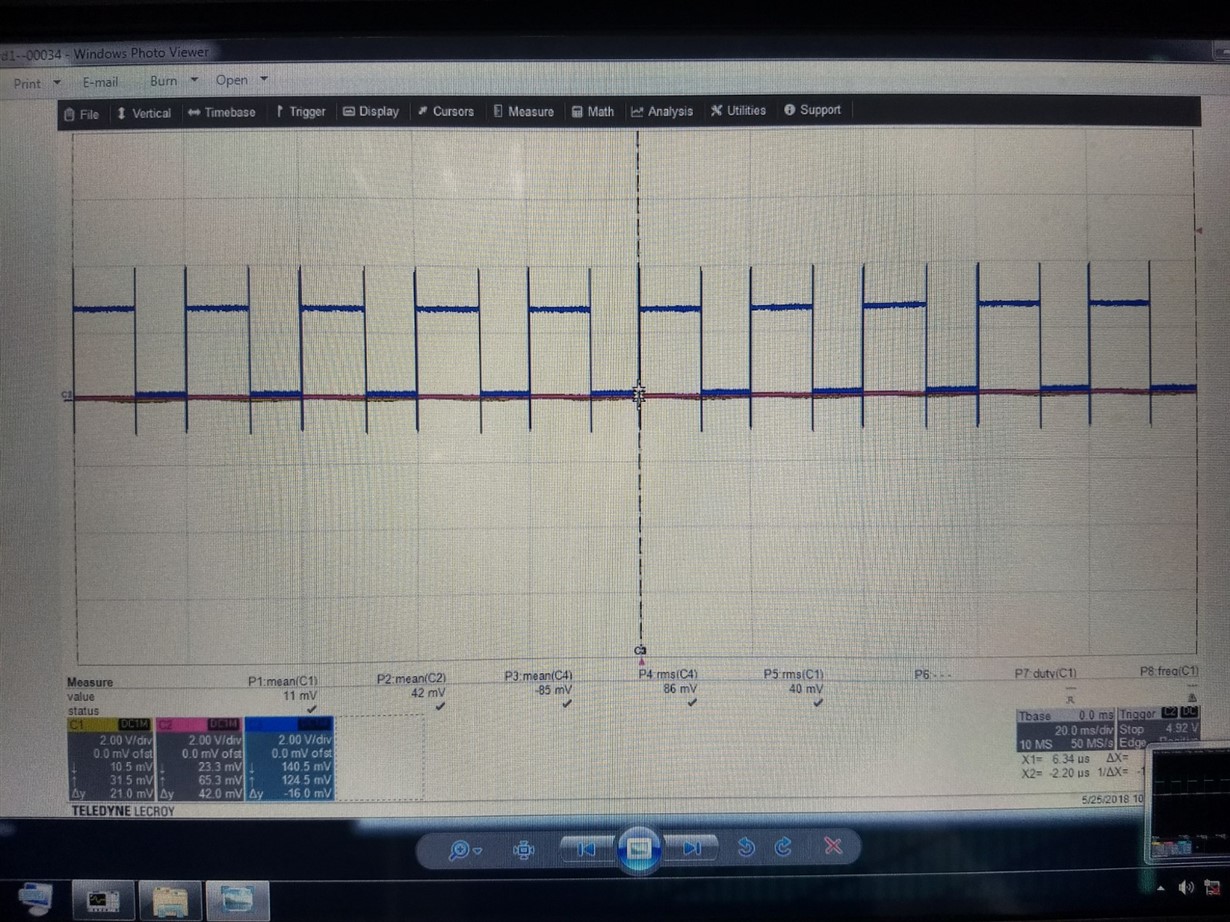

Also as per the datasheet when _OE is Low i.e 0V, the Output should be same as input. But in my device I am seeing it in reverse fashion. Why is it so?

Thanks and Regards

Arjun P Raj