Other Parts Discussed in Thread: TXB0104, LSF0108

Hi team.

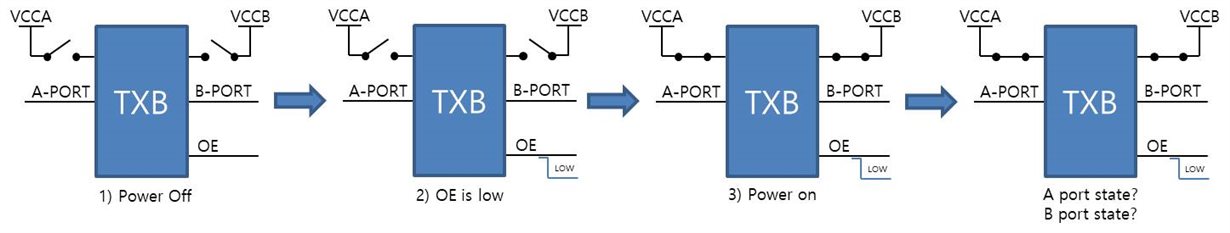

The customer requests data about the status of the output when the input is floating.

for example, if A1 is floating when input status, how is B1 status ?

Customers want products that are equally floating.

Additional inquiries

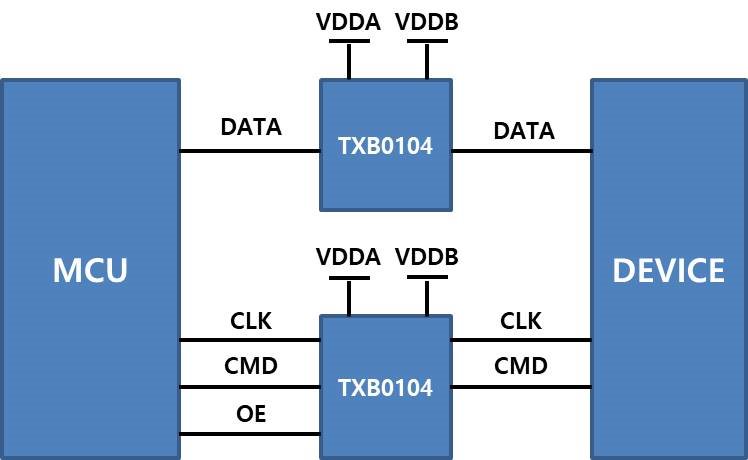

Is there a dedicated level shift IC for EMMC?

Please recommend if it is.