Hi,

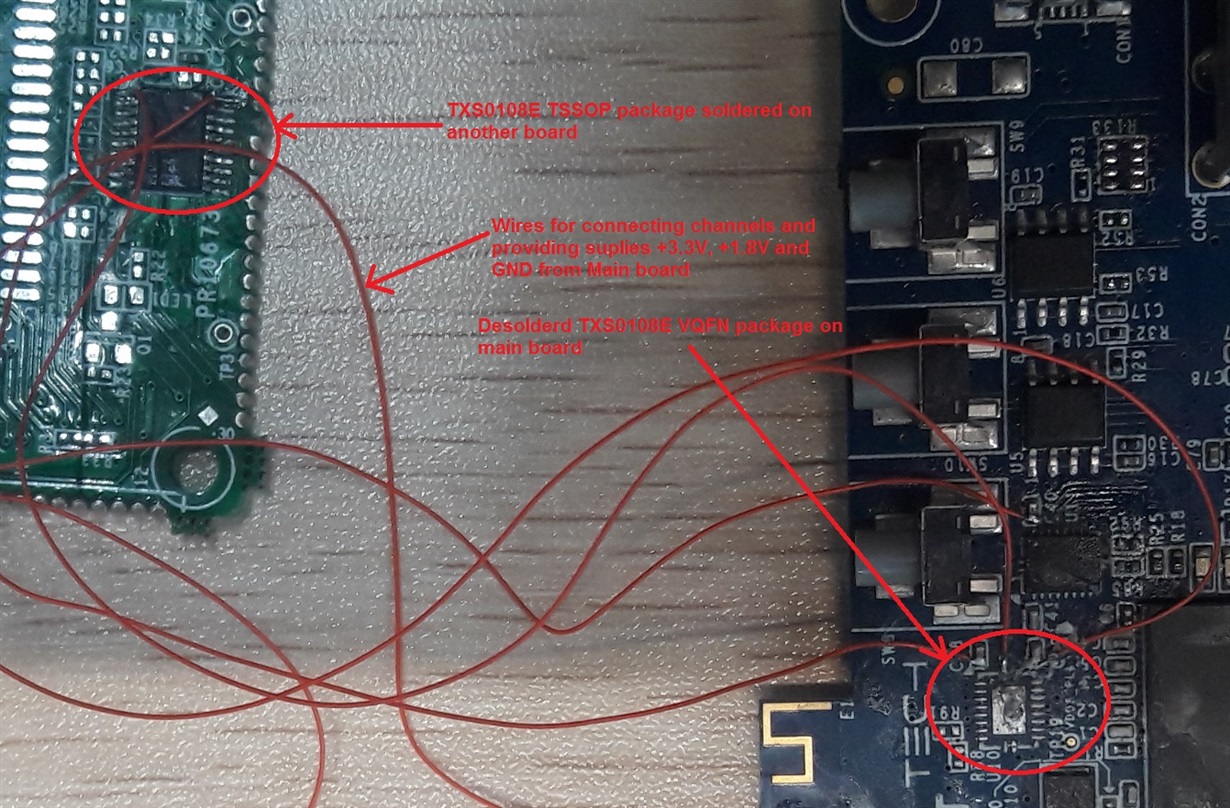

We are facing issue with the Level translation in TXS0108ERGYR IC. We are providing logic 1 (+3.3V) to one of the B channel pin(B1), we should get logic 1 (+1.8V) on corresponding A channel pin(A1) but unable to get it. Attached is the image showing the same of our our application.

Please let us know the whether we need to any other changes.