Other Parts Discussed in Thread: SN74AXC8T245

Hello,

I am Using SN74AVC8T245DGVR part in my project.

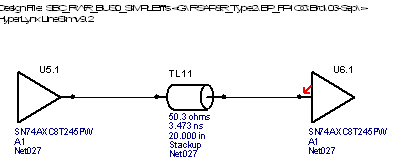

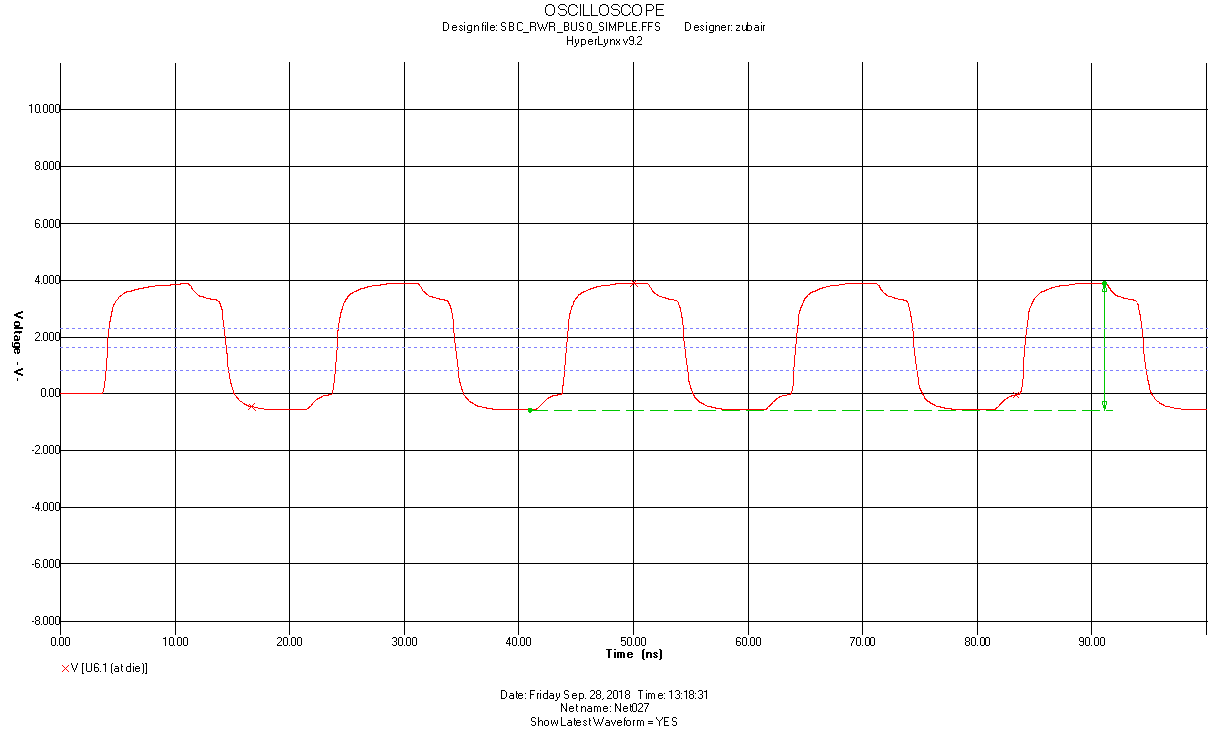

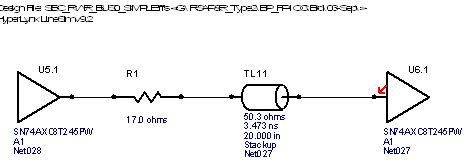

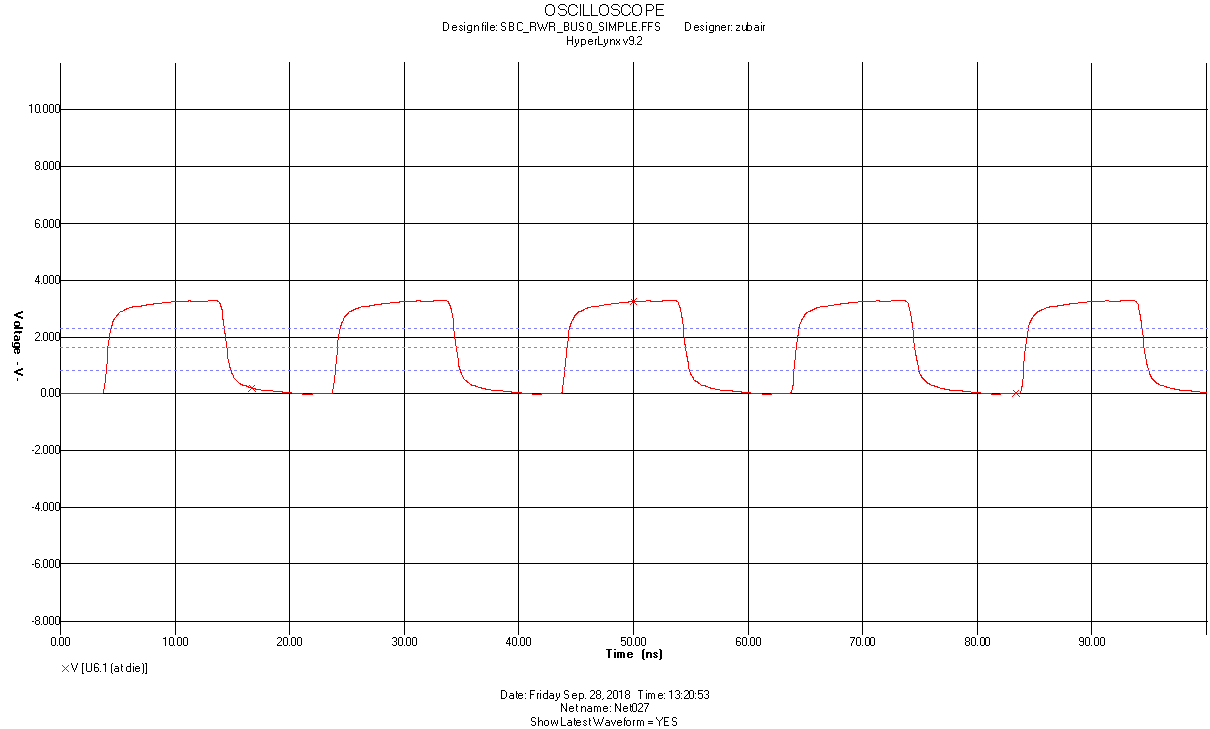

Actually this level translator output is connected to receiver section and having a trace length around 6.7 inches approx.

Operating speed will be 50 Mbps.

Can you please suggest what is the maximum trace length for this level translator??

Any terminations are required for this??

Regards,

Ramesh M