Hi team,

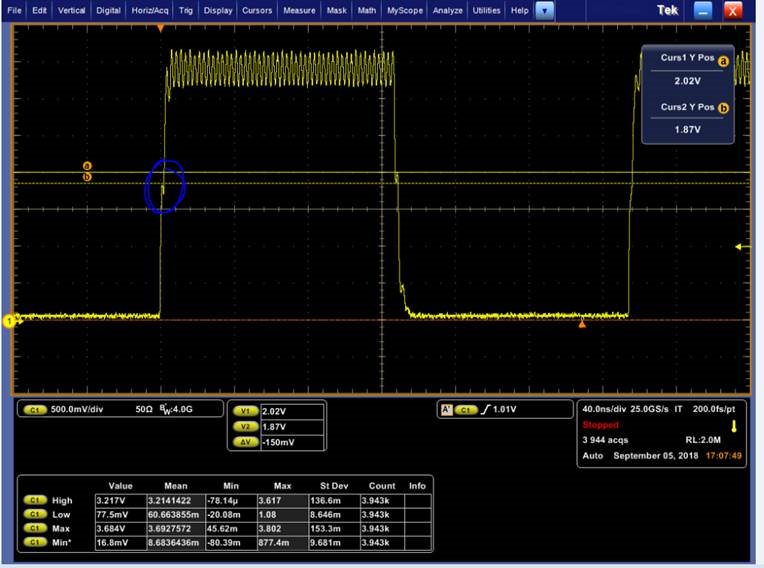

my customer is using the SN74AHC595 now. And we meet the drop of the rising edge. Whether it has risks.

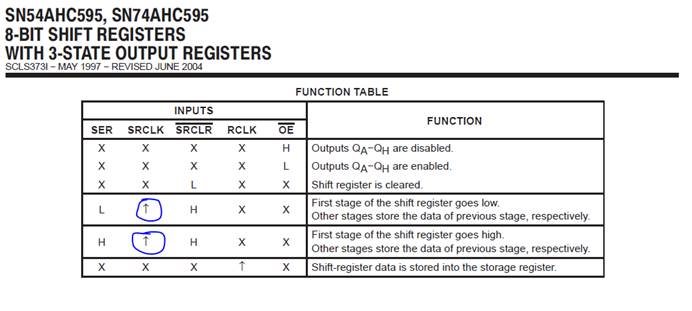

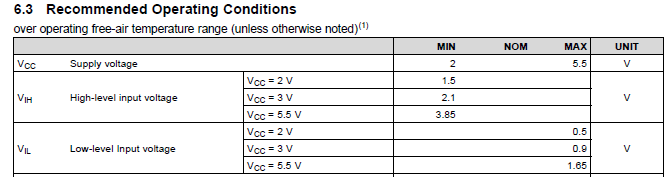

based on the datasheet, we get the devices CLK is based on the rising edge. i want to know how to decide the rising the edge. We calculate the Δt based on the

0V to 2.1v time, right? Thanks.