FAQ: Logic and Voltage Translation > Output Parameters >> Current FAQ

**** It's important to note that this FAQ is in reference to CMOS devices. Bipolar devices should not be paralleled in this fashion. ****

The primary concern with connecting outputs together is called "bus contention."

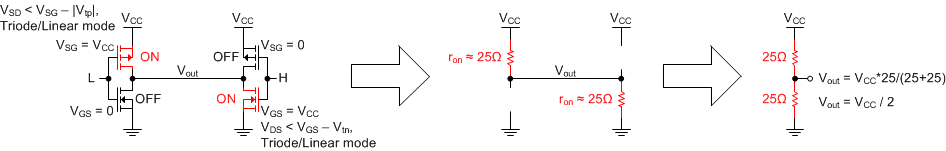

If one output is driving HIGH and the other output is driving LOW, then you have bus contention, and the device can be damaged. Here's an example with a fairly typical LVTTL driver:

In the above image, one CMOS output is represented as a single pair of nMOS and pMOS transistors. This is a very typical arrangement for CMOS outputs.

If we use a 5V supply for Vcc, it is easy to calculate the expected current as Iout = 5/(25+25) = 100mA. The current exceeds the datasheet absolute maximum for most logic CMOS outputs, and would likely damage the device.

It is possible to parallel channels of a device to increase drive strength -- it is just important to ensure that both outputs are always in the same state. The best way to achieve this is to use two channels in the same device, and to directly connect the inputs together to ensure they will always have the same state.