Other Parts Discussed in Thread: SN74LVT16245B,

We are using TWO number of 74LVT16245A chips to

buffer a0-15 address lines in one of the device, which is always enabled

and

buffer a16-19, RD, WR signals + d0-7 signals from another device

This device is controlled, and the direction of d0-7 is also controlled using RD signal.

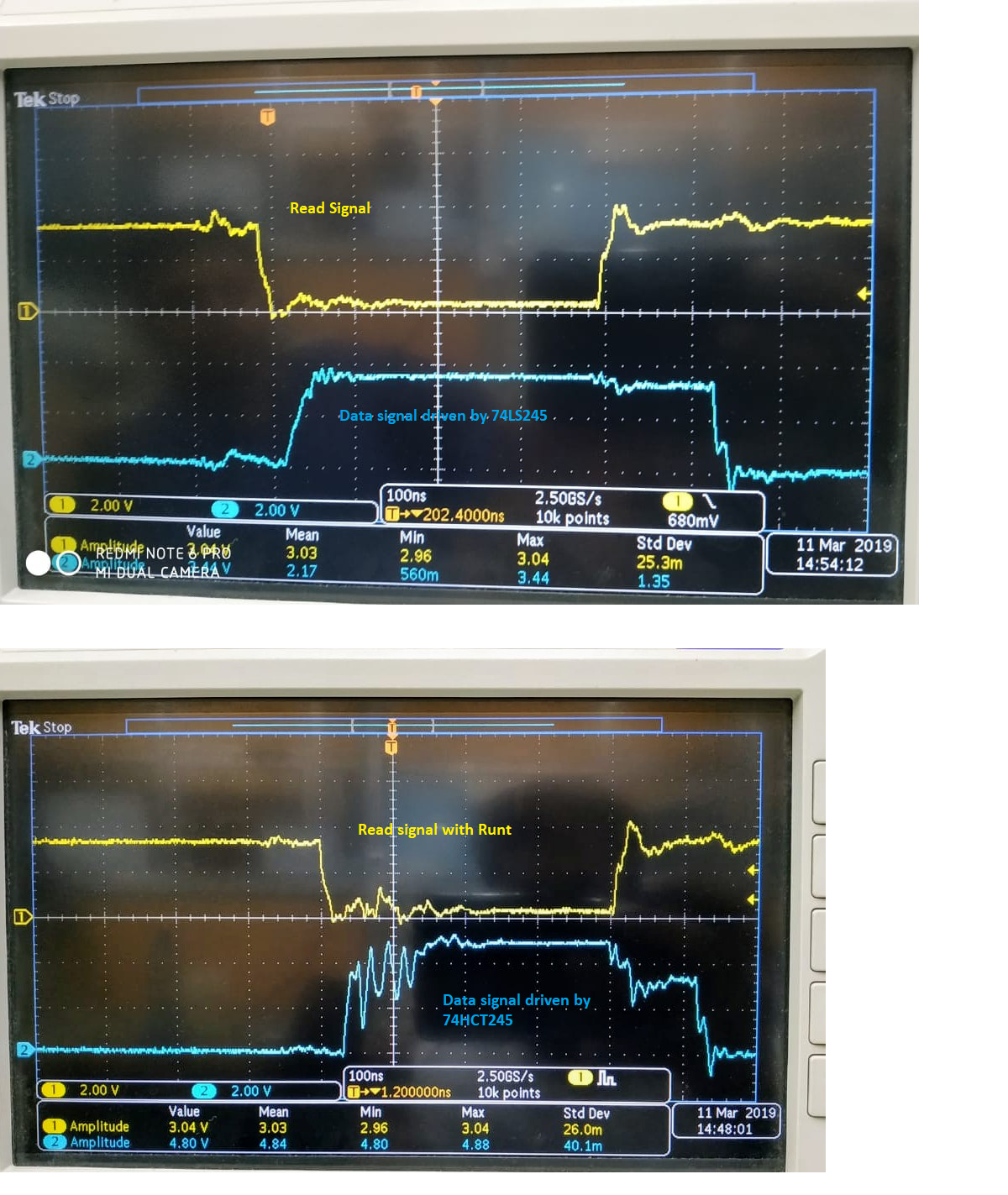

These are addressing 16 cards, having 22V10 PAL on A10-a19, 74hct245 on D0-7 and IDT7130 on a0-a9 + RD=WR

This scheme is working in system and addressing 16 cards from 2008 in the field.

When we recreated the same, [with new backplane and new PAL ATF22V10C-15PU]

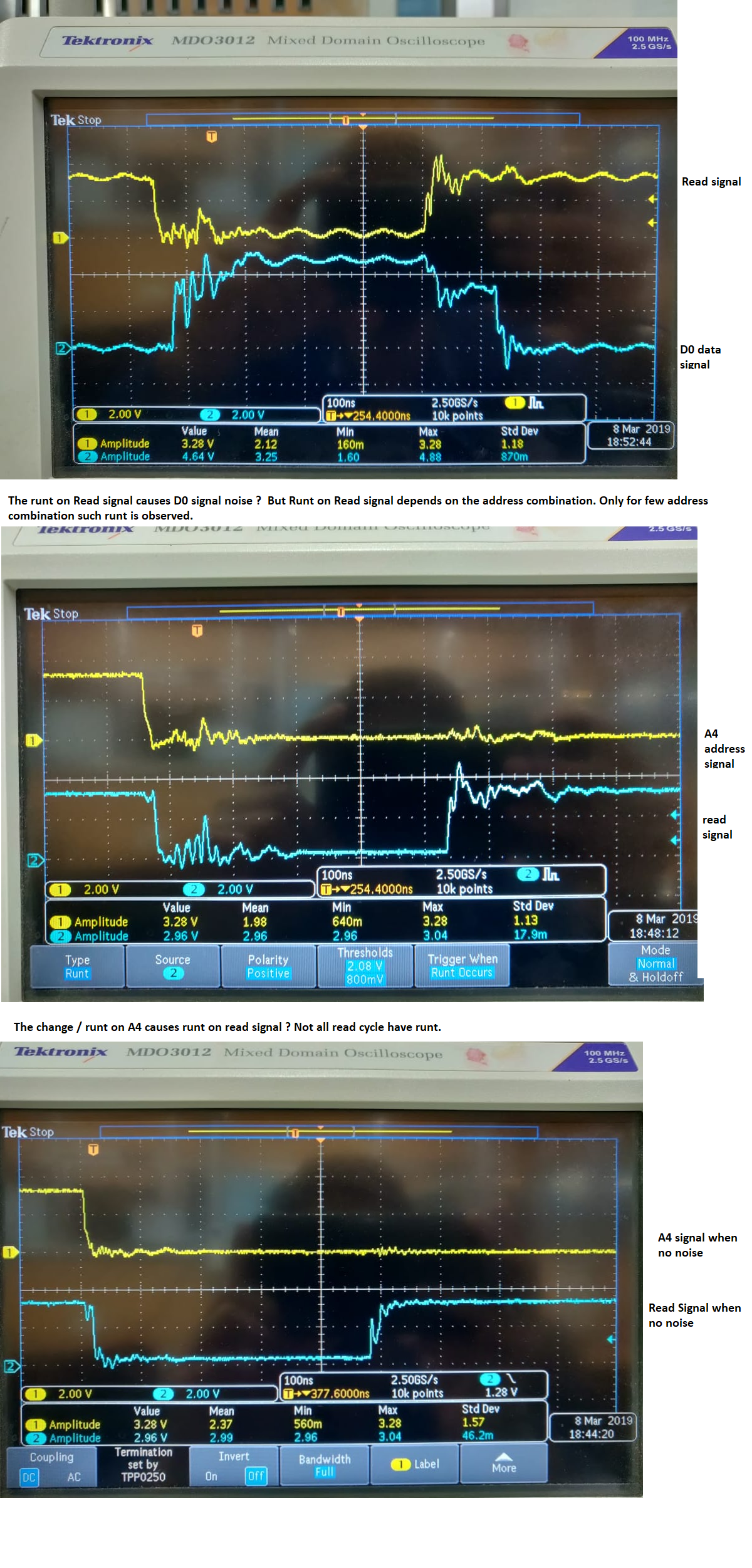

We are struggling for last 3 weeks, with spurious write taking place due to

1. ground bounce on a10-a19 which are used to generate CHIP Select signal.

The ground bounce occurs, when more number of lines change to 0. Like

address xx00 or xx80 or xxc0

or when data to be written is 00, 80, 40 RANDOMELY

We tried Termination from 220R to 10K

We tried Pull up from 2k2 to 10K

we tried pull-up 2k2+pull down 3k3

The problem remains same, it occurs once in 16000 or 40000 or 160000 writes.

How to resolve.

We checked with series resistance of 33R, or 68R or 220R, none helps