Other Parts Discussed in Thread: TXS0102

Hi team,

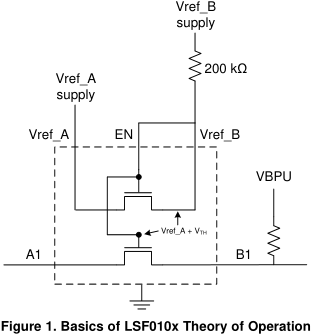

Do you have any guidance regarding active control of the EN signal? Specifically, the datasheet states that the EN needs to be connected to VREFB, and that pin pair then pulled to the relevant rail via a weak pullup, 200K Ohms nominal value. The datasheet also indicates that the EN signal, when driven LO, will disable the device. This leads me to believe that the EN signal should only be actively asserted by an open collector or similar driver. Is this correct?

I have two use cases which I believe are both bad.

The first case is where a push-pull driver actively drives the EN signal. I believe that a LSF0102DGEQ configured in this fashion would become damaged very quickly.

The second case is where an FPGA IO is used. The FPGA IO can assert the signal LO to disable the LSF0102DQEG device and then be tristated in order to allow the external 200K pullup to perform its function. I believe that in this scenario, the weak internal impedance of the FPGA IO would tend to interact with the LSF0102DQEG. FPGA IO impedances can vary widely from die to die, which would tend to lead to differing behavior between units.

Thanks.