Part Number: SN74LVC1G74

Hi,

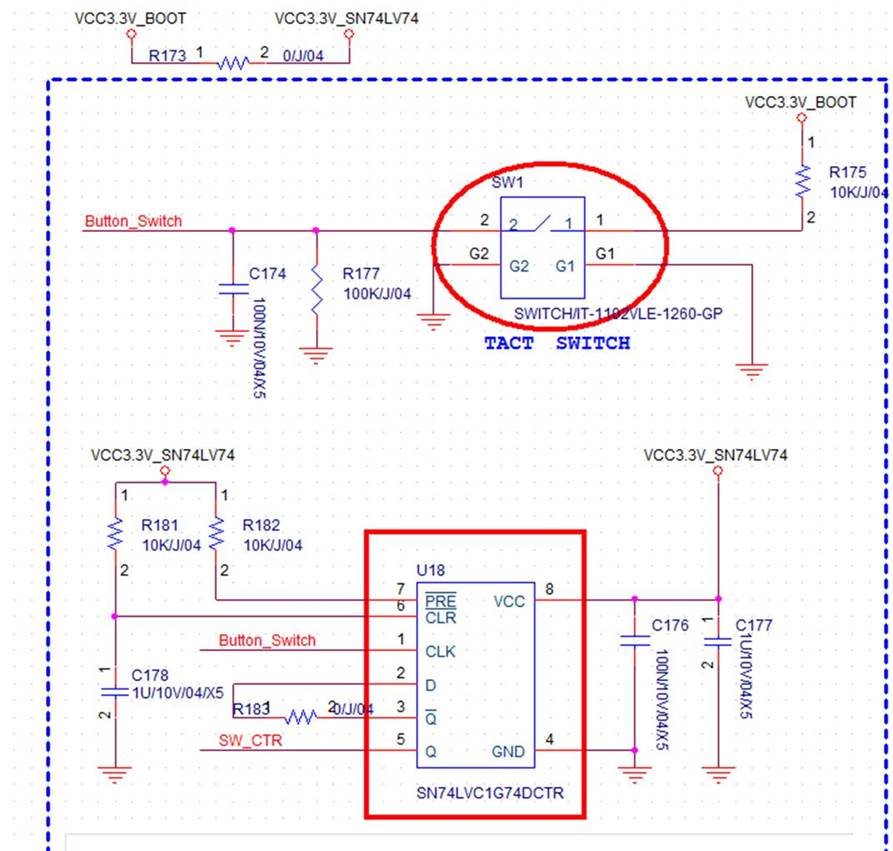

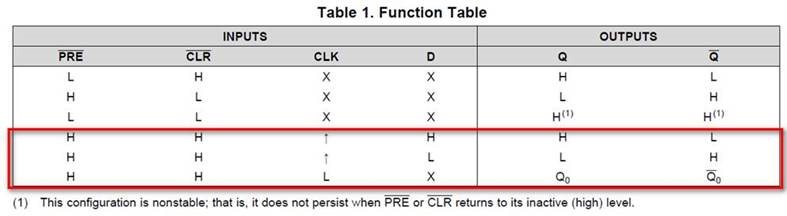

My customer is using this part for the power bottom trigger with below configuration, but even the clock is at falling edge, the output still change.

This does match with the truth table in the data sheet.

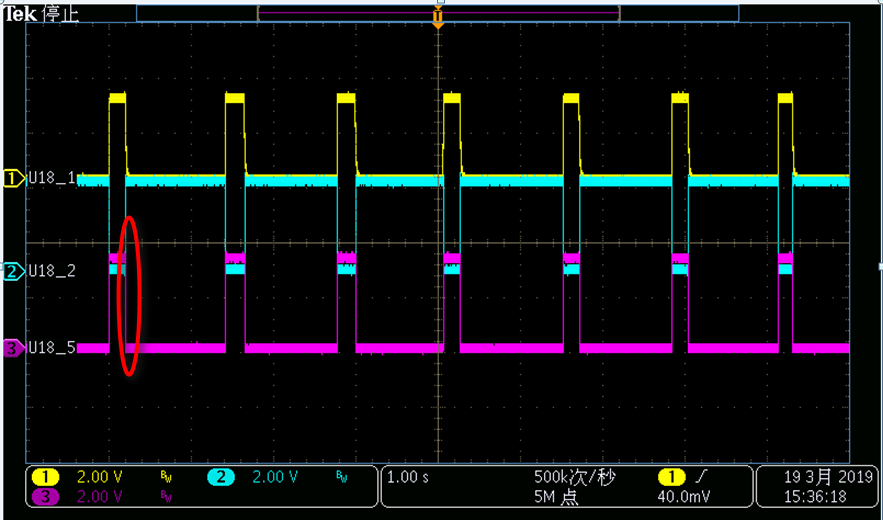

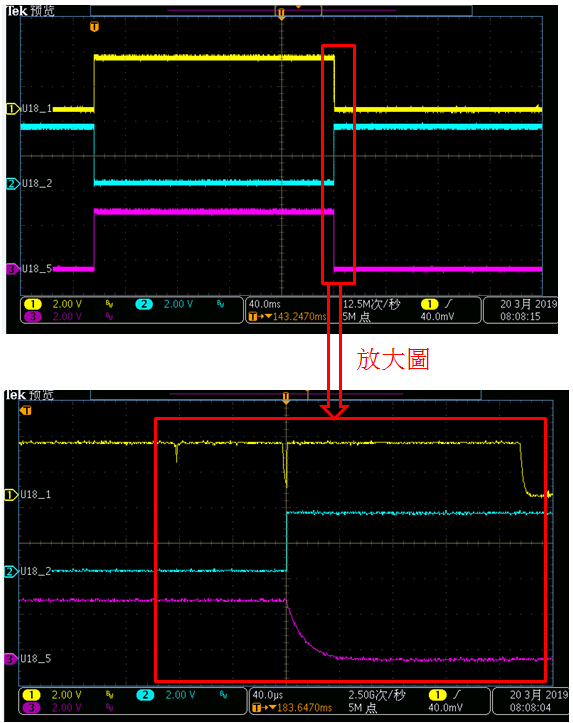

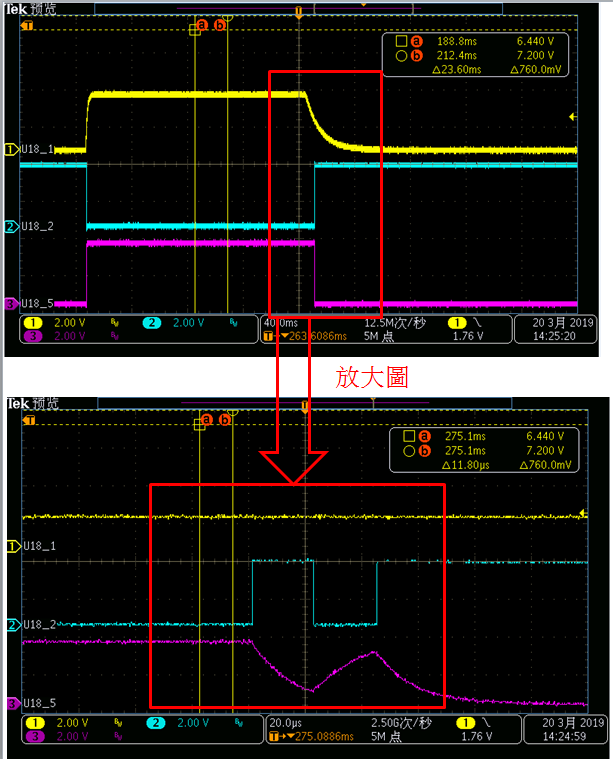

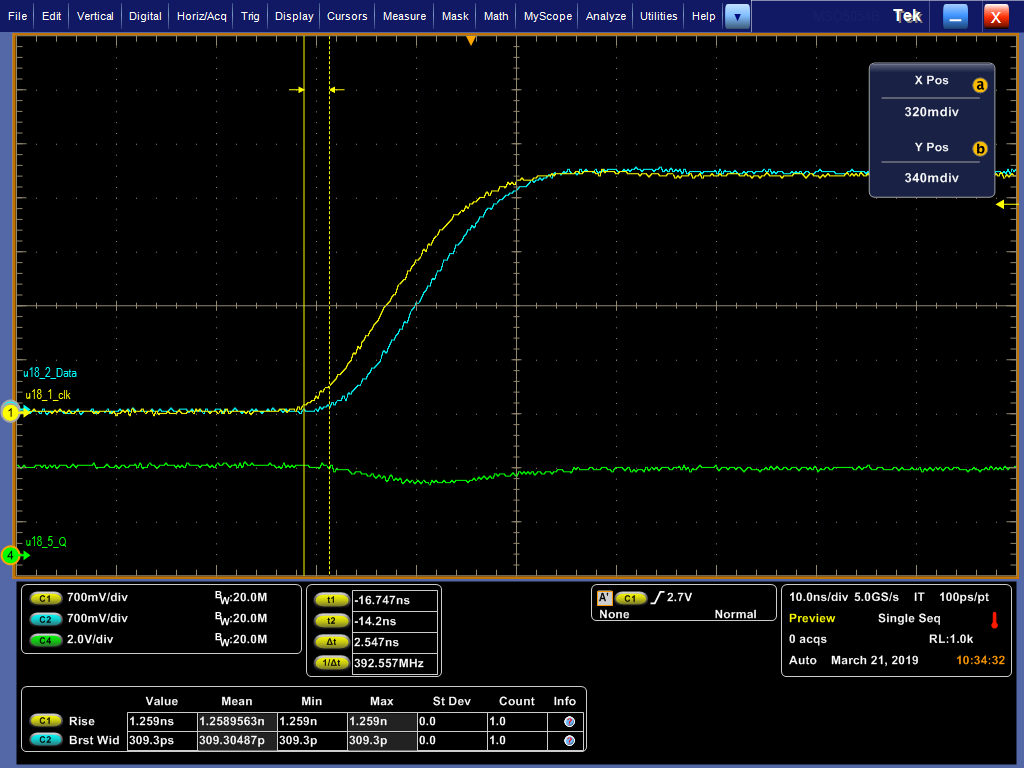

Abnormal waveform shown below:

Yellow: IC Pin-1 (CLK) ; Blue: IC Pin-2 (D) ; purple: IC Pin-5 (Q)

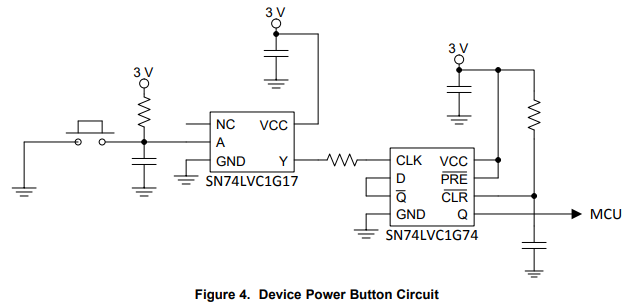

Please help to comment if there are modify needed of the configuration there are comments from your side how to deal with this problem and fix the behavior of this part.

Thanks for your help.