Other Parts Discussed in Thread: SN74AXC4T774

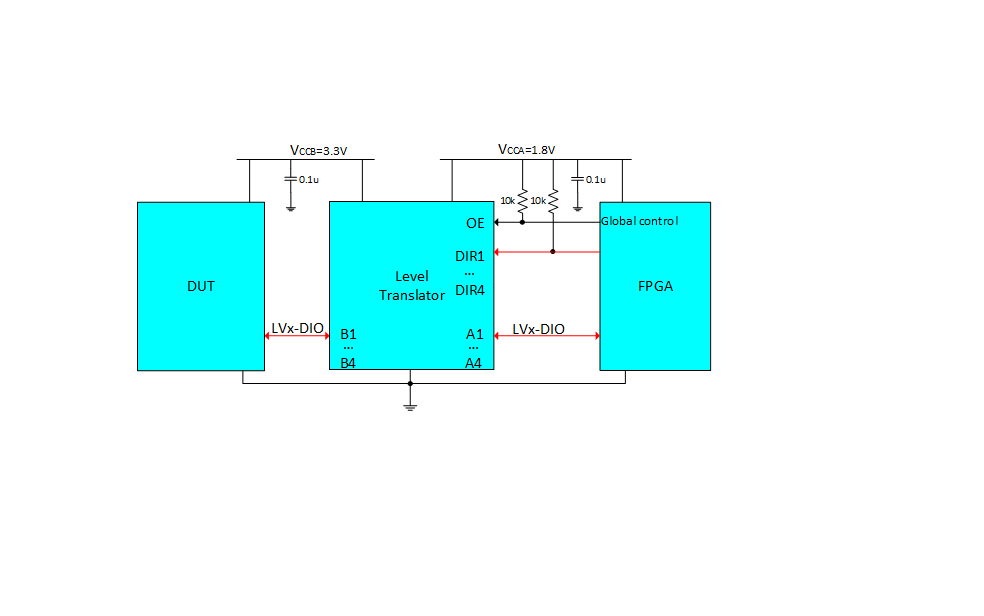

See the schematic above. SN74AVC4T774 is used for voltage shifting from 1.8V to 3.3V.

The requirements of this design proposal:

1. Bandwidth: >50MHz, so >100Mbps.

2. 1.8V is set as the same as the FPGA support voltage. But the VccB should be able to configured for I/O standards from 1.2V to 3.3V.

3. Bidirectional: Independent channel direction control.

4. Interface: 3-state is required in the data chain, because the DUT is unknown. Thus, it can be configured for PU or PD by DUT. The PU/PD resistor is not allowed in the Level translator.

SN74AVC4T774 is available for high speed >100Mbps, 1.2V-3.3V voltage range, individual DIR control pin. Only one OE pin for high-Z set High before power up/down completed.

Requirements 1&2 is OK, but there are some QUESTIONS in 3&4:

3: My design need to read the information back during the data transfer. Thus, the direction will be changed during the running.

In some TI's datasheet, the level shifter with DIR control pin. The device required to disable the device at first, then set the DIR, after this enable the device again. Is it necessary to enable and disable the SN74AVC4T77? Can I set OE to LOW during the normal operation, then during the running, I set the DIR for bidirectional functions without any limitation?

4. I saw some discussion in the forum, the input is always active. Thus, the PU/PD is required for the SN74AVC4T774. Is this used for low power consumption?

But for my design, as we talked before. The logic level should be set by the unknown DUT. It can be High or Low. We can not make a PD/PU on the Level translator.

The worst case will be: direction from DUT to FPGA (B-A), DUT is no signal maybe floating (software maybe can set it for LOW for idle), no PD/PU on SN74AVC4T774. Will this be a big problem?

Kind regards

Rongpeng Zhai