Hello support team,

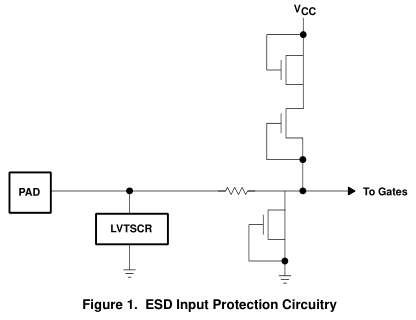

The customer want to know the input protection circuit (ESD diode) characteristic on SN74AHC1G86.

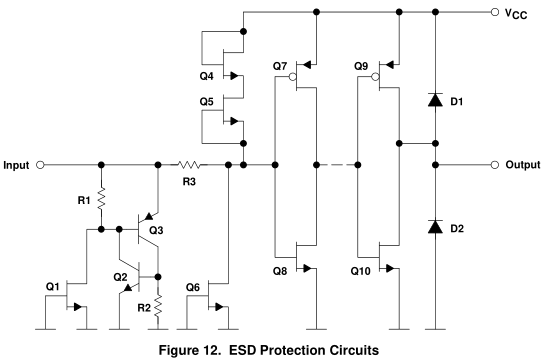

Is the input protection circuit can clamp the plus direction over voltage and also the negative direction over voltage?

The customer needs to know how much current is allowed to both directions and also needs to know how long time is allowed. (Allowed pulse width.)

Because on the customers system the input voltage may have a possibility to go less then GND voltage (go to minus voltage) then asked.

I think in case of above the customer should need to add the clamp circuit externally but not sure the exact things. Please give us your feedback.

Best regards,

Izumi Maruyama