Other Parts Discussed in Thread: MIO

Hello,

I am using TXS02612 as SD Card voltage-level translator with a Zynq-7000 Xilinx FPGA. The Xilinx Answer Record AR# 63913 (Zynq - Marginal SDIO timing on ZC702 and ZC706 can lead to data CRC error while initiating write to SD device) advise for a "possible violation of the 2.0ns input hold time as defined in the SDIO specification" when using a voltage-level translator. To resolve this issue, "SD_DAT[0:3] and SD_CMD lines must be lengthened to compensate for the maximum channel skew as specified in the level shifter data sheet". (www.xilinx.com/.../63913.html)

This recommendation is also in the Xilinx Zynq-7000 SoC PCB Design Guide (UG933 - Section MIO/EMIO IP Layout Guidelines - SDIO (v1.13.1 p.68)).

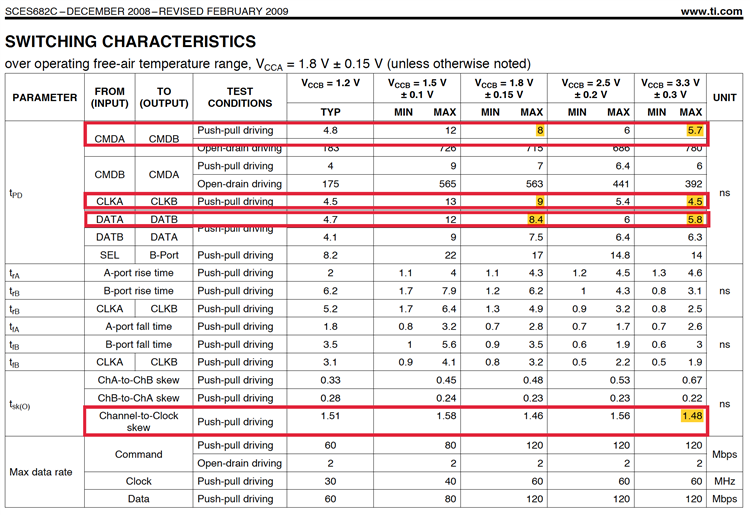

When I look at TXS02612 Datasheet switching characteristics for VCCA=1.8V (Table at p.12), tpd(max) from Port A to Port B for CMD/DAT is not necessarily higher than tpd(max) for CLK.

- When VCCB=1.8V, tpd(max) for CMD (8ns) and DAT (8.4ns) is smaller than tpd(max) of CLK (9ns).

- Inversely, when VCCB=3.3V, tpd(max) for CMD (5.7ns) and DAT (5.8ns) is higher than tpd(max) of CLK (4.5ns).

From those characteristics, one could conclude that in some conditions, the buffer Channel-to-Clock skew could be positive (buffer delay higher for CMD/DAT than delay for CLK) and in other conditions, the buffer Channel-to-Clock skew could be negative (buffer delay smaller for CMD/DAT than delay for CLK).

In order to properly compensate for TXS02612 channel skew on PCB:

- I need to know for VCCA=1.8V/2.5V with VCCB=3.3V, if the Channel-to-Clock skew (tsk(o)) given in the datasheet is always positive i.e. that the buffer delay of CMD/DAT ports is guaranteed to be higher than buffer delay for CLK port?

Thank you.