Other Parts Discussed in Thread: SN74AXC8T245, TXB0108

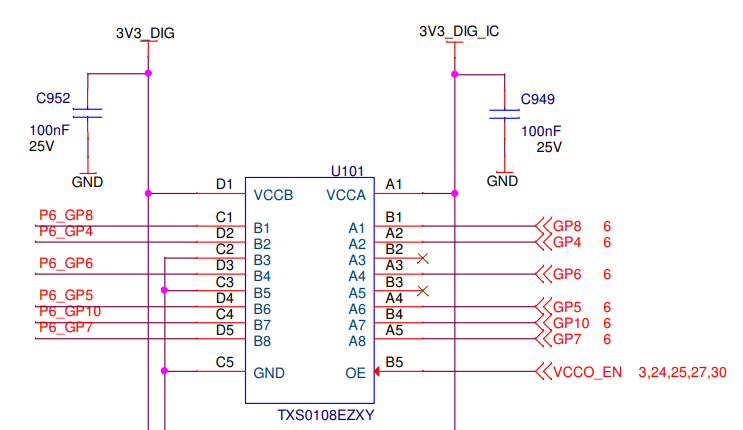

I'm using the device as a buffer between an external GPIO connector and an FPGA. The FPGA and VCCA are both powered by 3V3_DIG_IC, which is internally generated on the board and is nominally 3.3V, and should be reasonably accurate (within 1 or 2%).

VCCB and the external GPIO are powered by an external power supply that can be 3.3V +-0.3V. Obviously this can create a situation where VCCB could be 3.0V, and VCCA= 3.3V. I have the option to lower 3V3_DIG_IC to 3.135V, but can't really go lower than that.

The datasheet gives no tolerance for VCCA being higher than VCCB, so is there any safe value for VCCA to go higher than VCCB, even if it's as low as 0.135V, or will this be enough to damage the device?