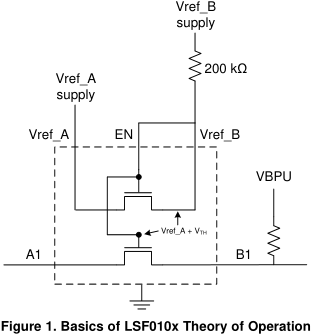

I would like to clarify exactly how DOWN translation operates and what the need for the pull-up is on the lower voltage side. In my example I have a bi-directional 3.3V logic CMOS gate with a separate direction pin and I am translating that to an FPGA pin operating in a 1.8V bank. VrefB and EN is tired to 3.3V through 200k. VrefA is tied to 1.8V.

When the B side gate is driving a logic high, near 3V, my understanding is that the internal 4-terminal FET will be ON as long as the B side voltage is less than 1.8V. This makes the A side follow the b side up to 1.8V. Then when the B side signal crosses 1.8V, the FET turns OFF. If a pull-up is connected on the A side o 1.8V, this will allow current to be supplied to the FPGA input from 1.8V after the FET is OFF.

Is my understanding correct so far?

The data sheet and application video state the pull-up to 1.8V is optional provided the A side gate is not leaky. But if the signal is in a steady state high, and NO pull-up on the 1.8V side (A side) is included, then does this design count on the input capacitance to hold the level at 1.8V? IS this reason why the input can be too leaky? It seems like a conservaoive design would include pull-ups and not count on receiver input capacitance to hold the charge.

Please clarify my understanding.

Thank you

Craig