Other Parts Discussed in Thread: SN74AXC8T245, SN74LVC8T245

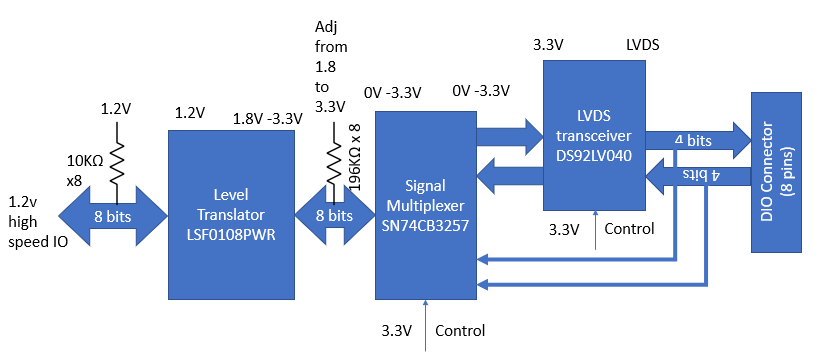

1) A circuit is needed to accept any kind of logic between 1V to 5V (we will vary the pull-up voltage accordingly) and interface to an 1.2V IO, I proposed this one, any proposal for the value of the resistors? Consider highest rate up to 400 MHz if possible …

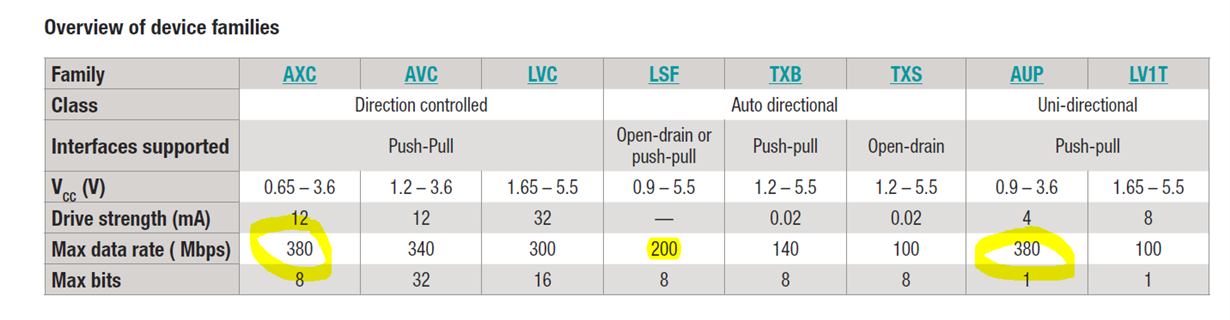

i look at the level shifter selection guide.

it seem to me, the max data rate for LSF family is only 200Mbps. Am I right to say the closest family that i should used are Direction controlled/uni-directional level shifter as circle above AXC or AUP family. Any recommendation for the proposal for the value of the resistors?

Best regards,

KPK