Hello

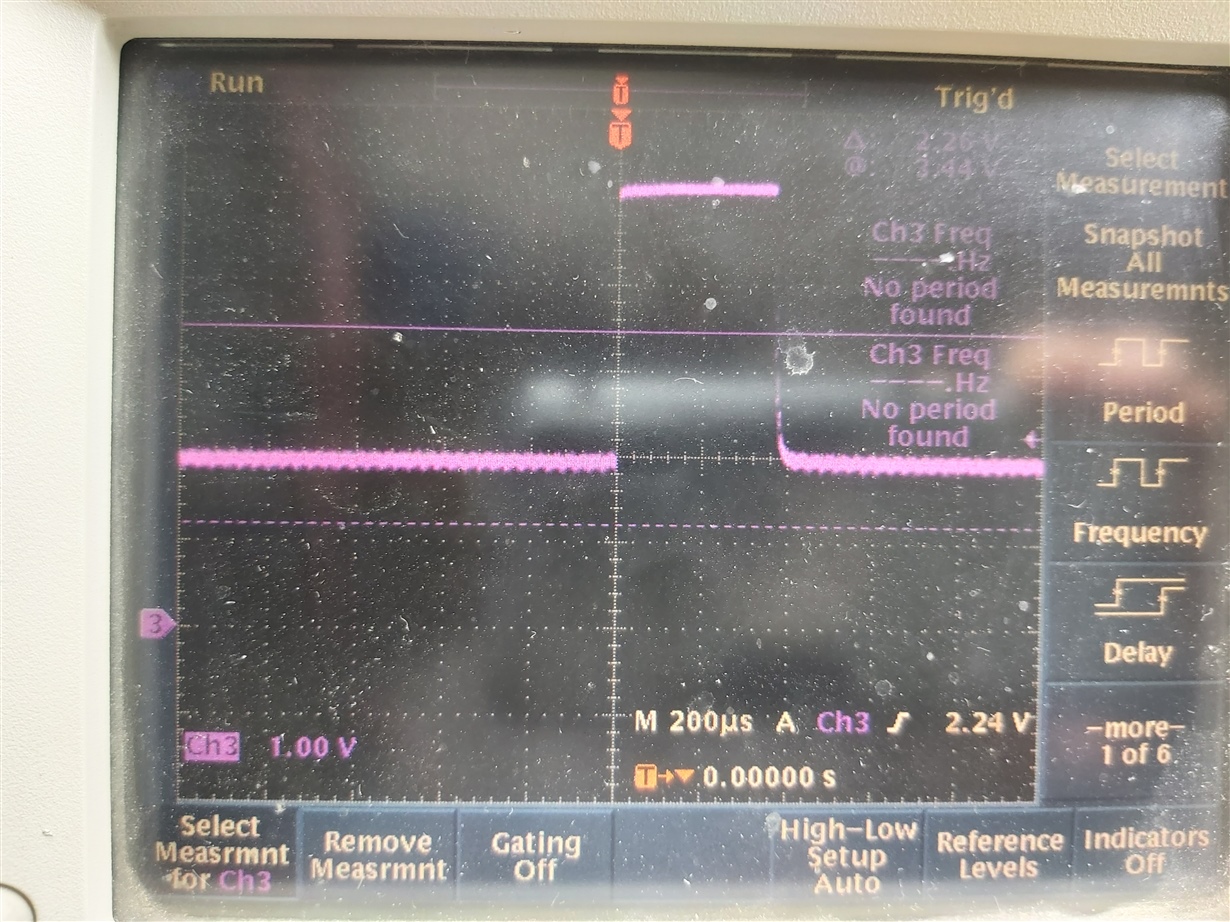

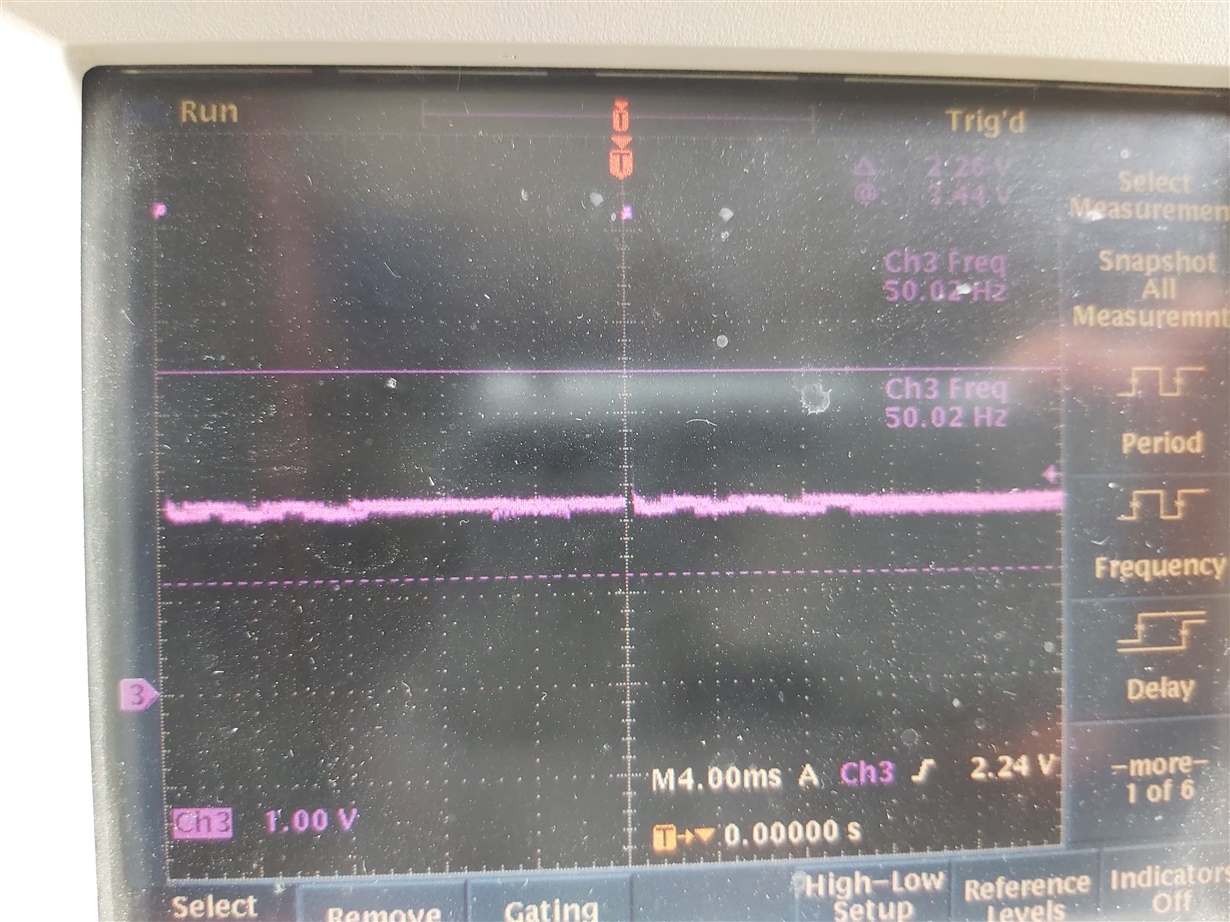

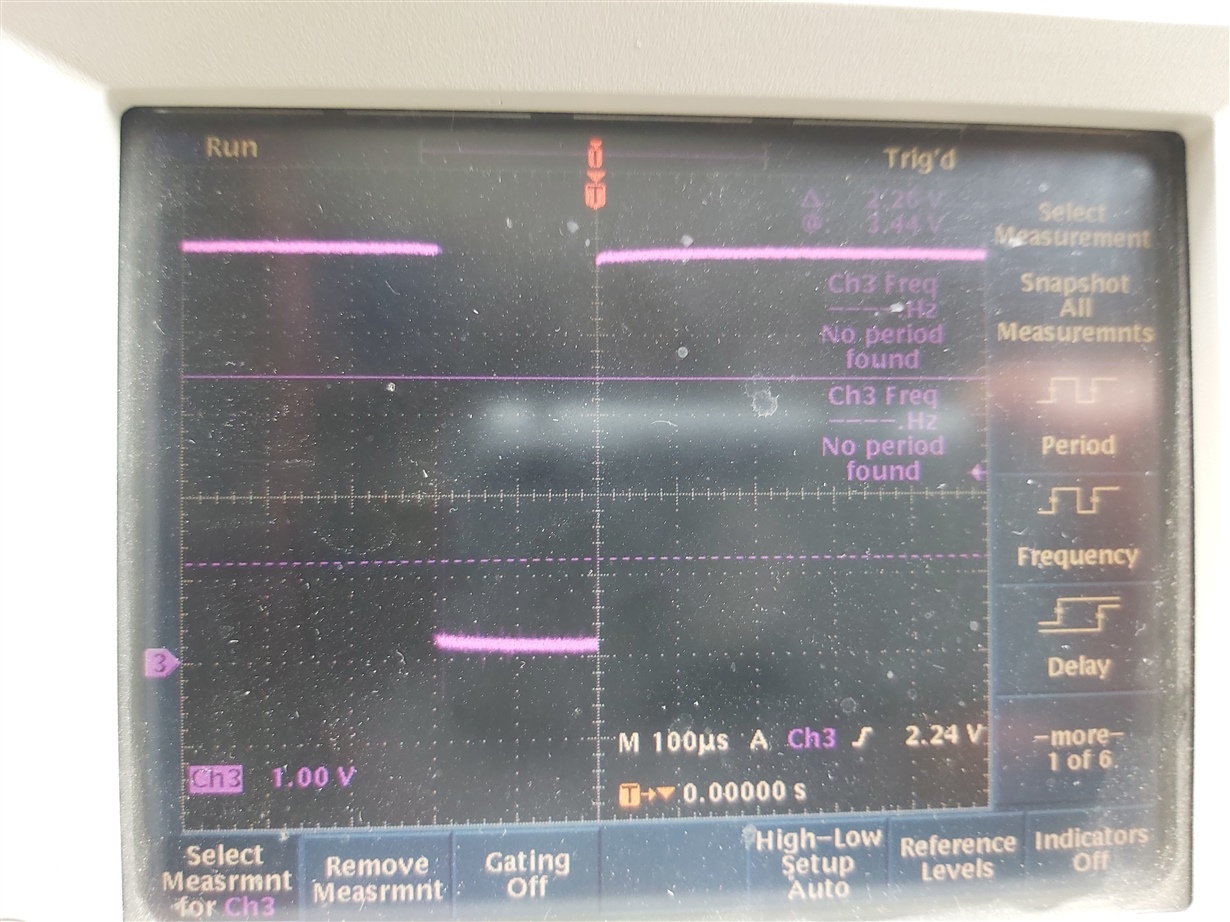

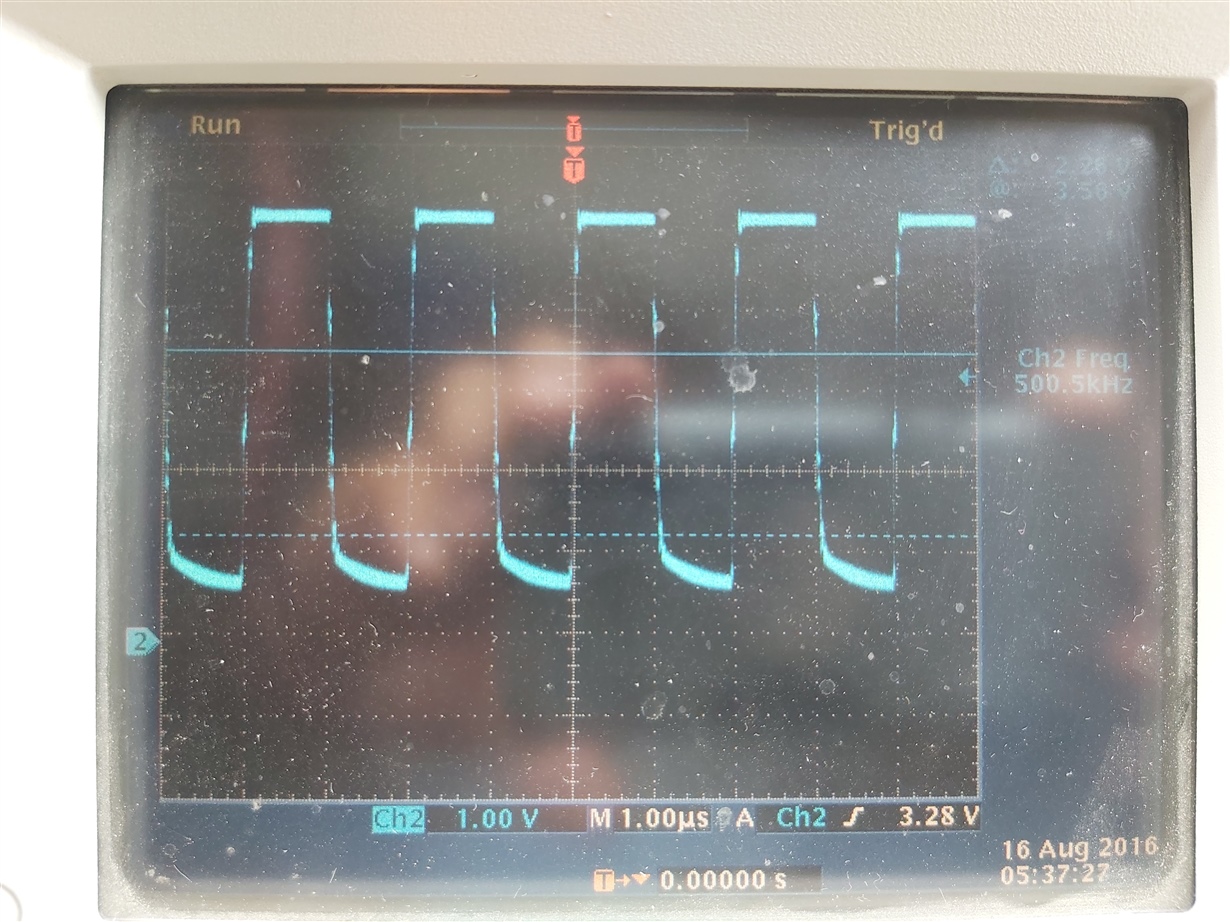

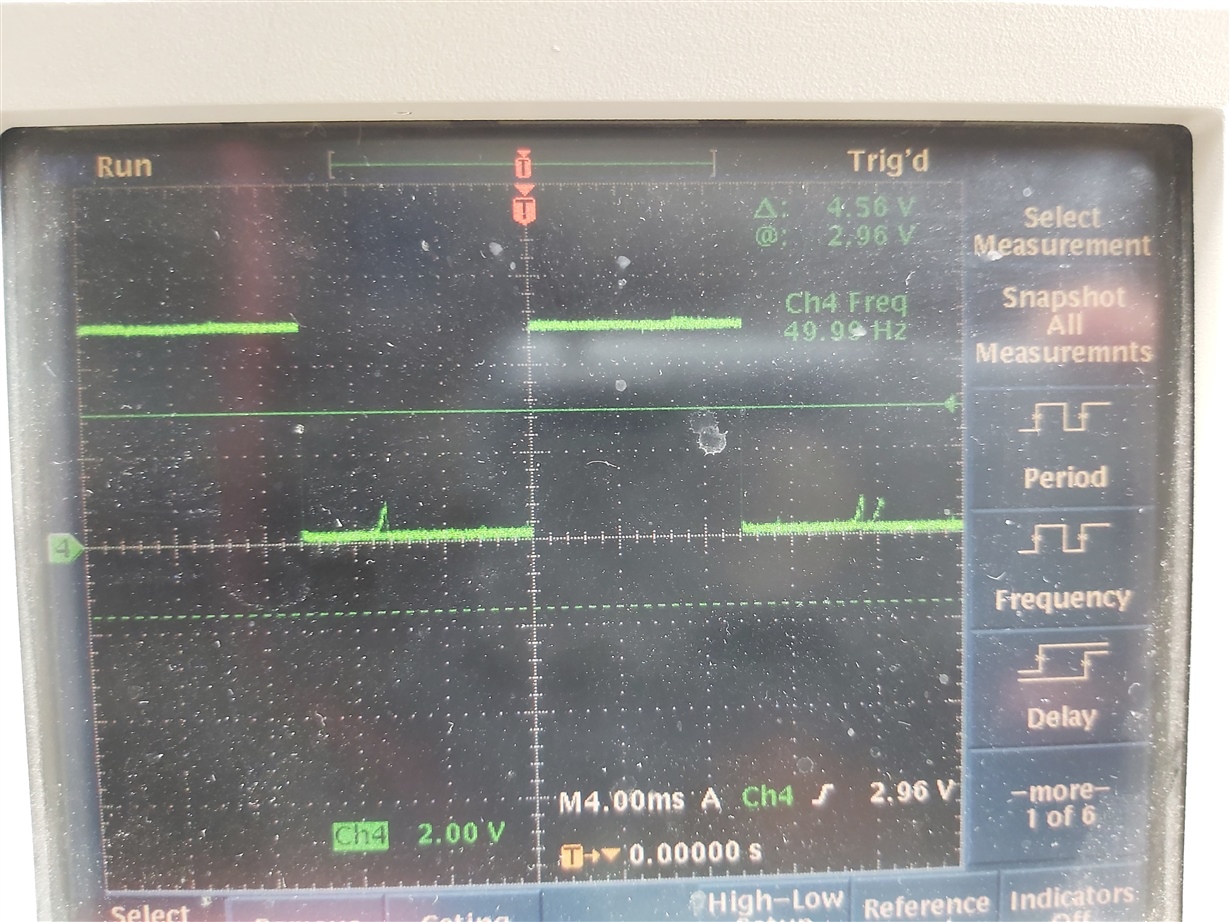

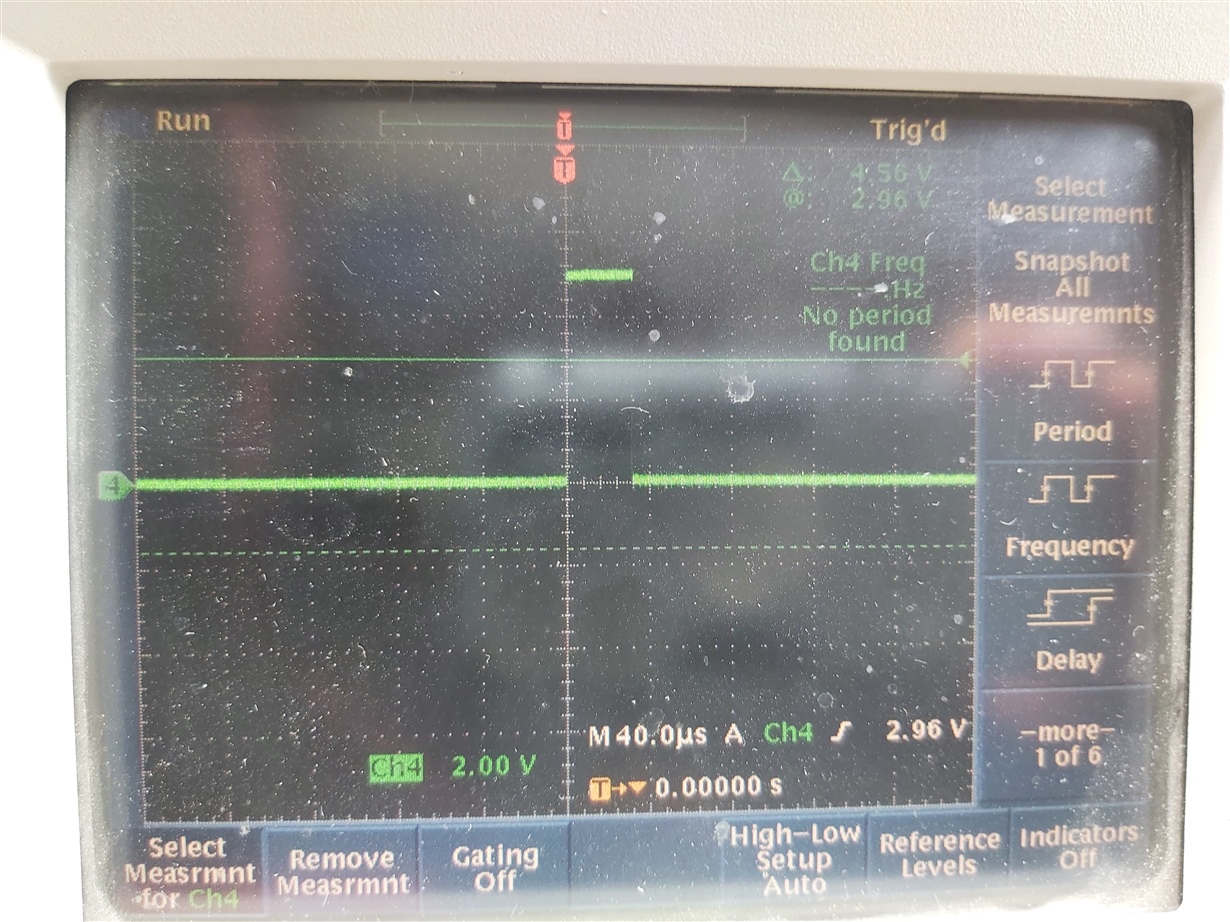

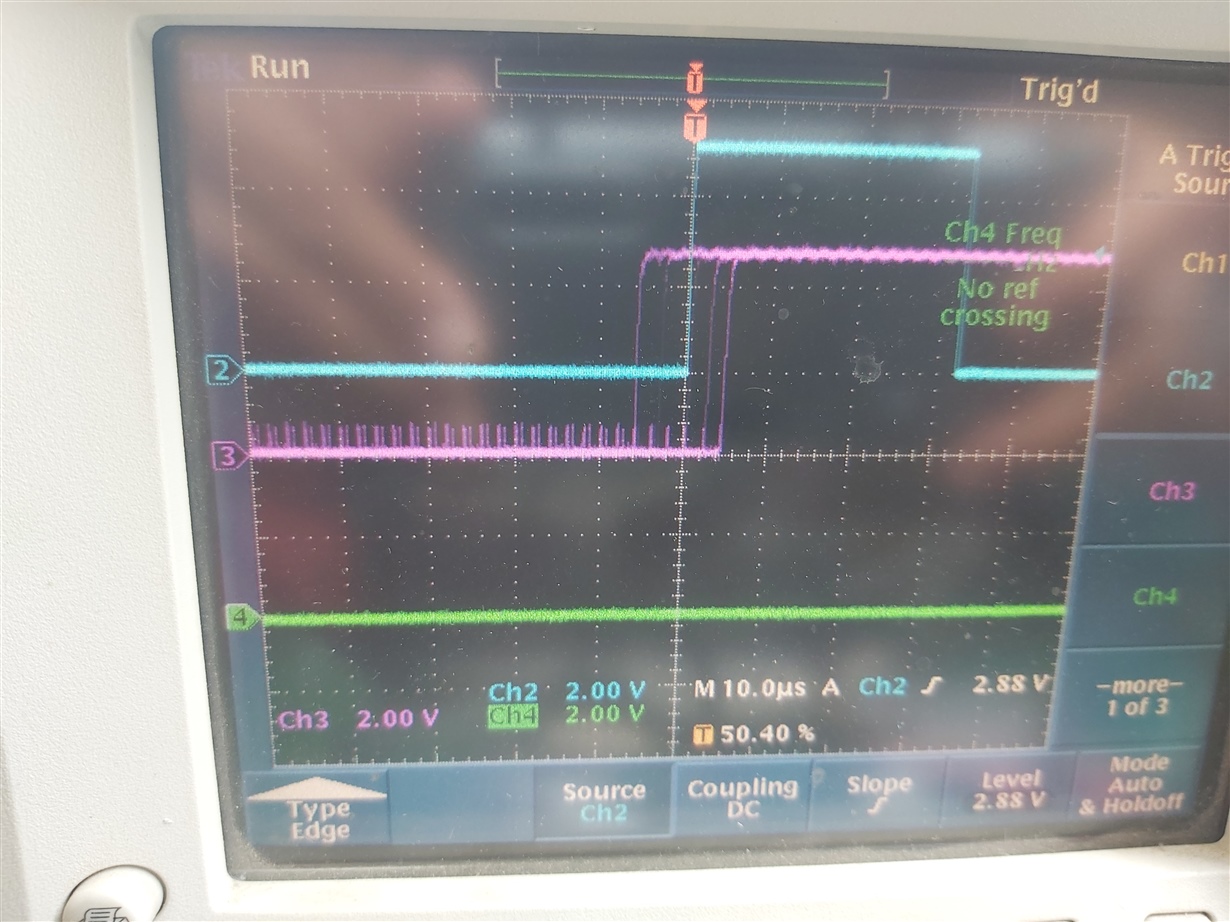

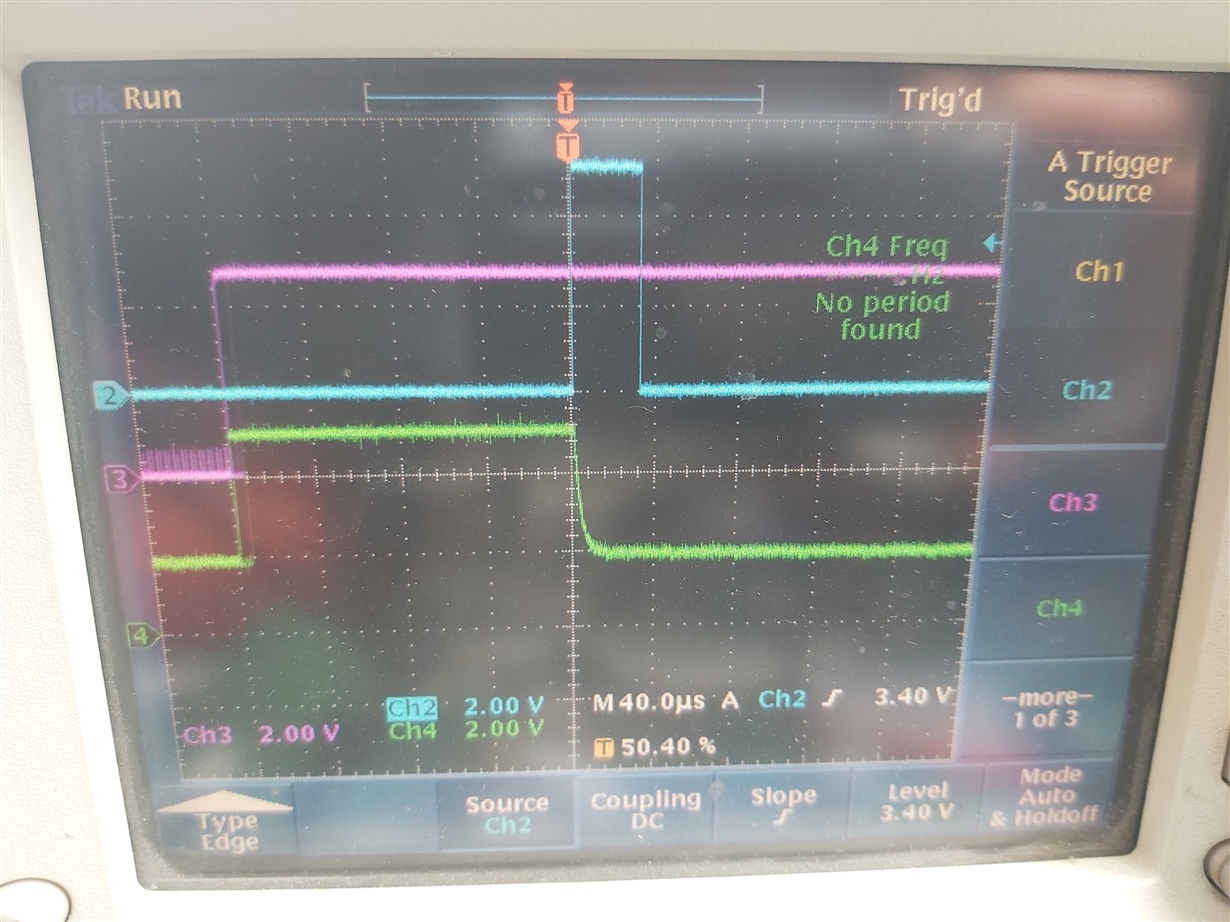

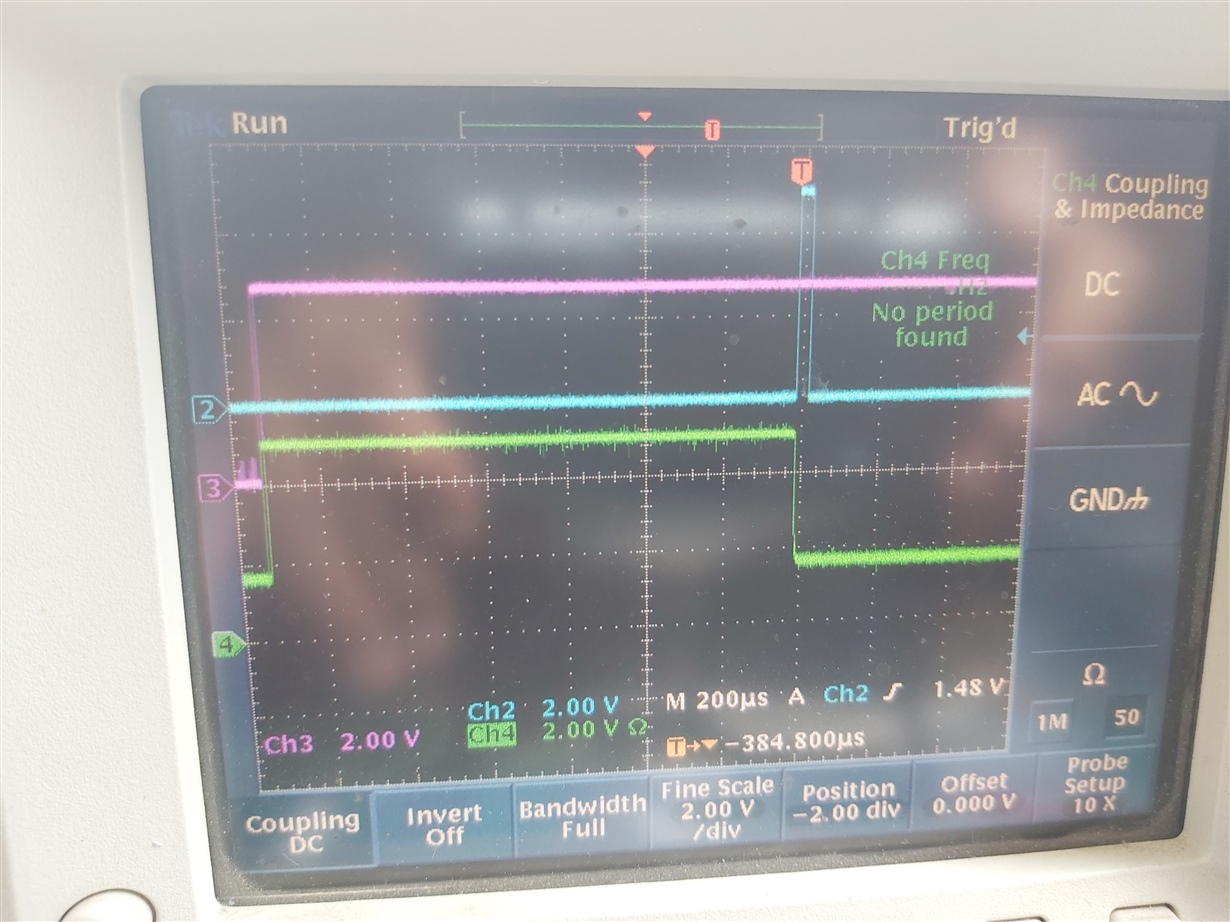

I used R1-270K, R2-220K, C1-100PF to get 500KHZ, I want to lock the frequency to the mains (50HZ).

I did a frequency division and I used PC2.

Can you help me calculate LPF values?

(R3, R4, C2).

Best Regard

Itamar

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.