Part Number: CD4050B

Other Parts Discussed in Thread: CD4098B, , CD4013B

Hello

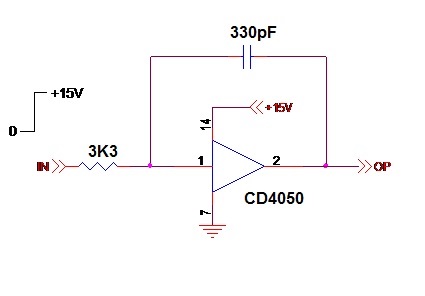

I wish to use the following Ckt for a Min Pulse width creation for our Three Level Inverter.

Four such Ckts shall be used per leg. Approx 800 nS to 1.1 uS is the target Pulse Width

for both On & Off.

PS is +15V and Input Signals too are 0-15V.

I have the following queries:

1. At the Negative Transition point, the Input would be momentarily pulled below Gnd

where the internal Clamping Diode shall reset the 330 pF cap thru the Rdson of the O/P Stage.

Is the Internal clamping diode ( to Gnd ) good to take this repetitively?

2. At the Positive Transition point the Input shall go above the +15V.

Would it be destructive for repeated pulses?

3. If I choose to incorporate a Series Diode at the Input, either end to +15 & Gnd

but do not insert a limitaing Resistor with the 330 pF Capacitor, would that be okay?

Thanks and regards

Varun