Hello,

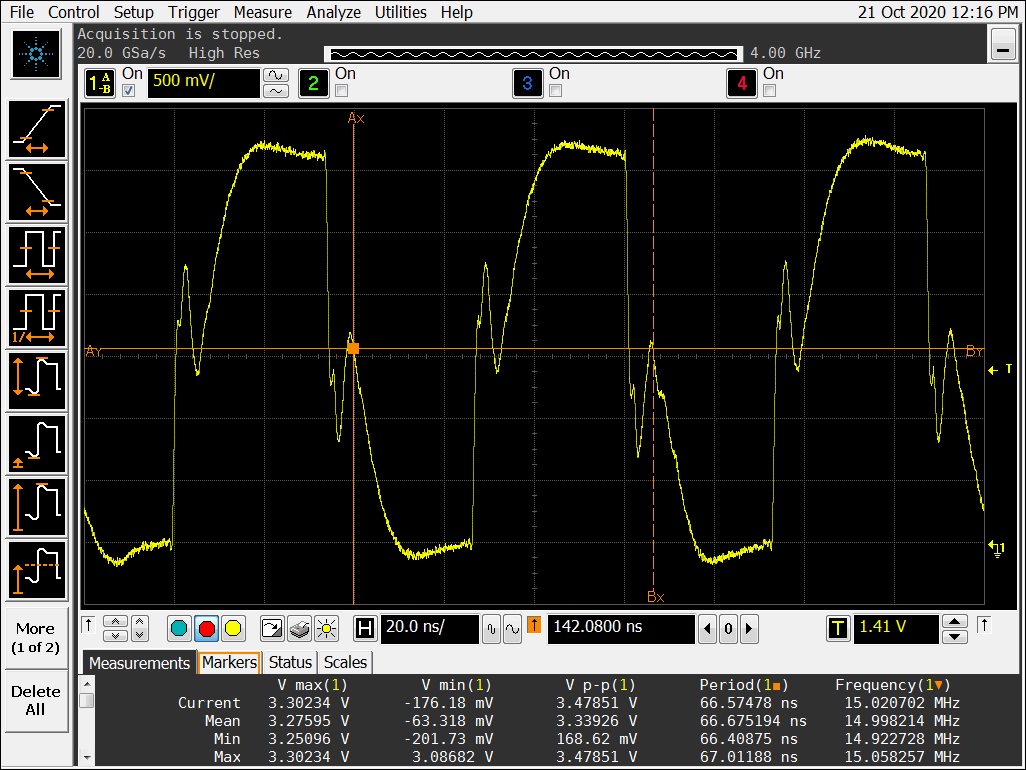

I am having signal integrity issues in one of the Buffer outputs. I`d like to understand what could be causing it ? Some incorrect implementation? Do the 2 buffers inside the chip work differently?

Attached the schematics and Buf(2) images. The same was observed t 3 different samples.

I assumed it could be an impedance mismatch and changed the series resistance R1405 to 0, 22, 27, 30, 33, 46 and 75ohm, but it did not solve the problem.

Thanks,

Jhonathan