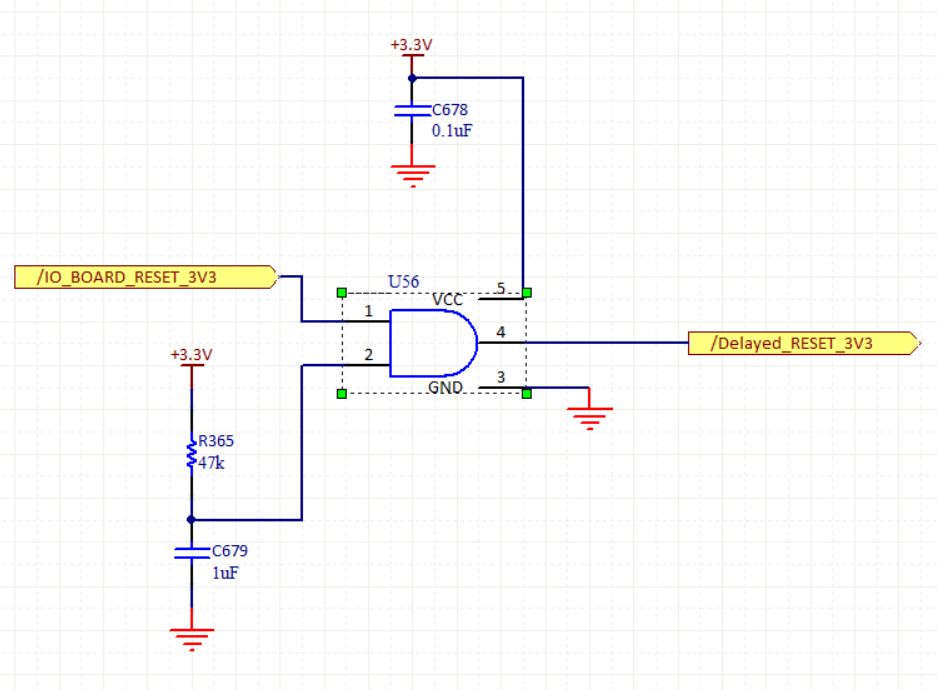

Other Parts Discussed in Thread: SN74AUP1G97

Hello,

I have a Schmitt Trigger AND gate I am using for timing at reset. The inputs to the AND gate are one digital, and one RC timing circuit. I am not measuring much noise on the RC input and the line does not appear noisy until the oscillations happen. The oscillations eventually stop after a few microseconds and the output goes high.

Things I have tried so far:

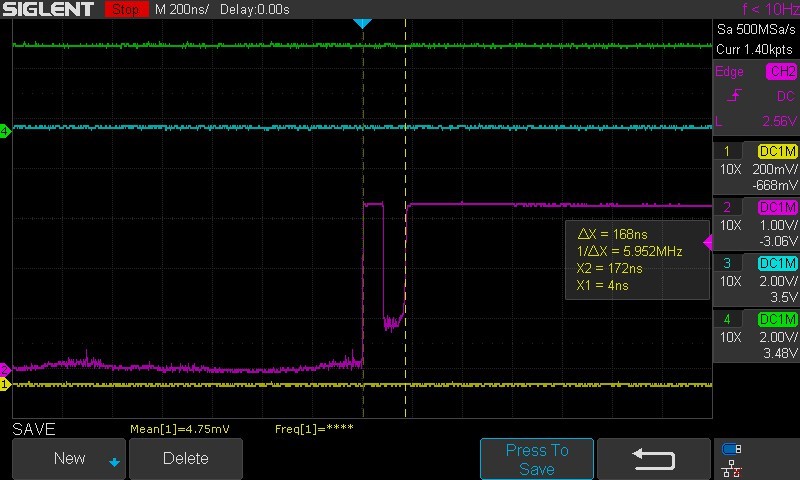

1. Putting a 0.1nF, 1nF, or 10nF capacitor in parallel with the 1uF timing capacitor. There is no difference in output with any of these parallel capacitors.

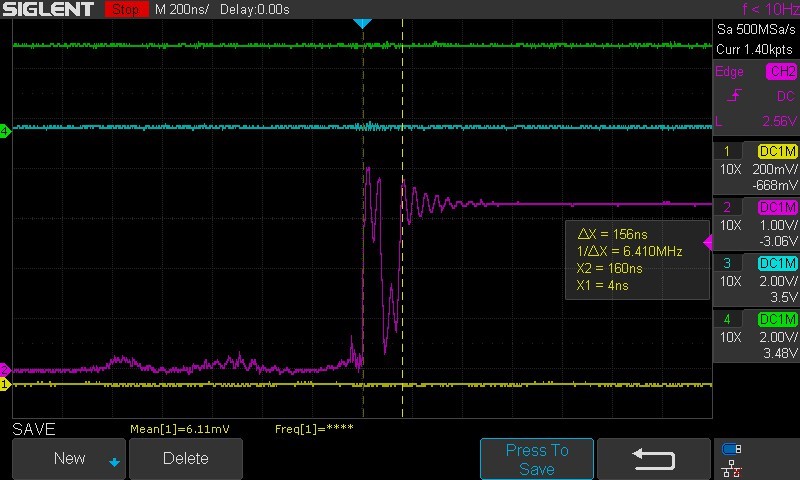

2. Lifting the output pin and measuring the signal when it is not connected to the board to eliminate any possible reflections/impedance mismatches. The oscillations are then removed, but a single low pulse follows the low to high transition.

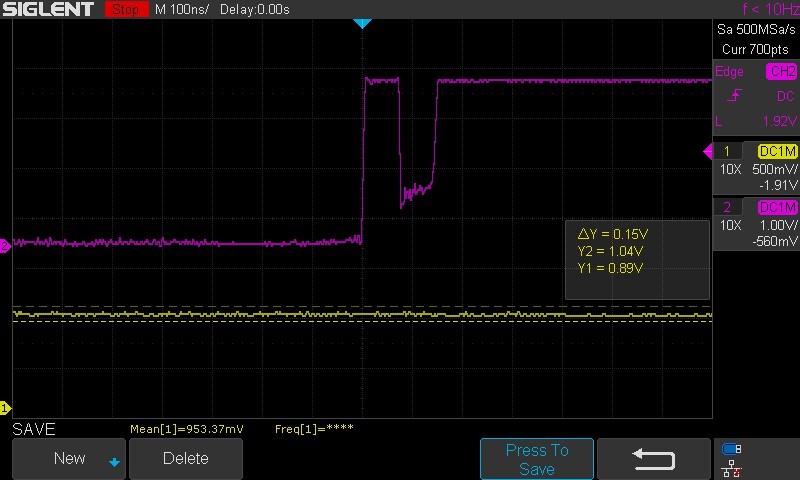

The frequency of the oscillations are about 25MHz. The width of the first high pulse is 150-170ns. Please see attached schematic and oscilloscope captures.

Thanks,

Matt

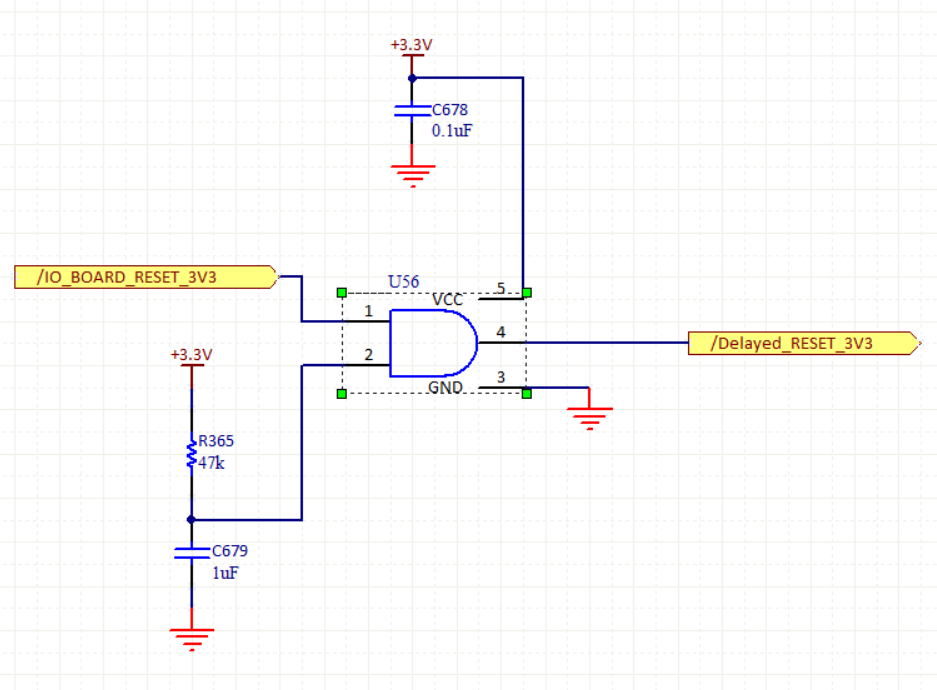

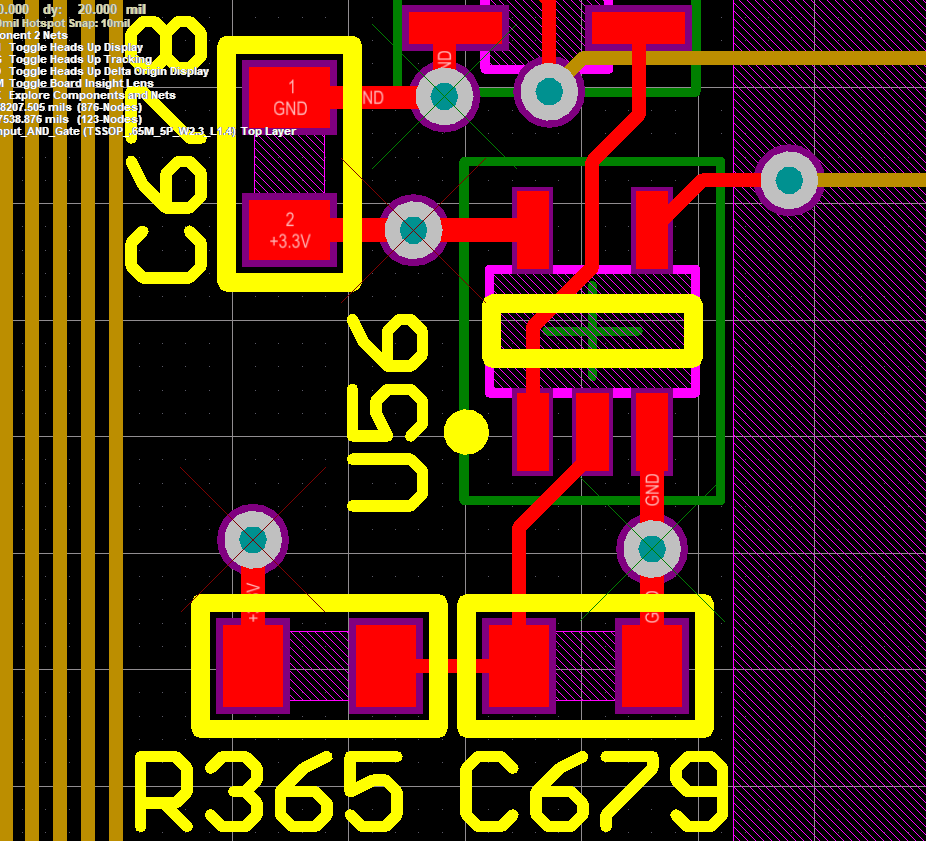

Schematic:

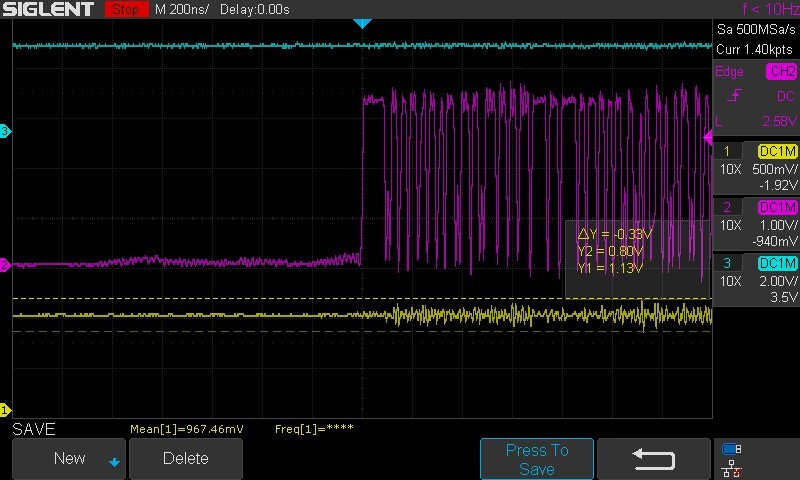

Original scope capture of the problem. The purple is the output pin, the blue is the other AND input (digital), yellow is the RC timing input pin.

Scope capture of the output pin lifted. Purple is the output pin, green is the other AND input.

Scope capture with the output pin lifted and a 0.1nF capacitor in parallel with the 1uF timing capacitor.