Dear Sir/Madam,

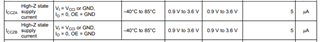

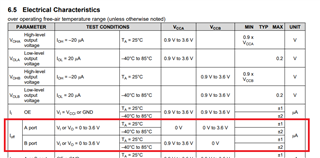

Please help to confirm with TI TXB0304 datasheet of the Ioff below as per spec table below.

Does it means the leakage current?

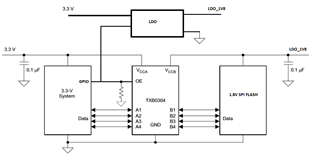

With application circuit below, the highlighted red above in the table is it correct leakage current for our case?

And for highlighted red above, A port mean for 1 port leakage or total A ports leakage?

Which leakage is suitable for our case from the spec if above highlighted leakage is not for our application circuit? Main reason for asking, we have the send the part for FA and the result is NO fault found.

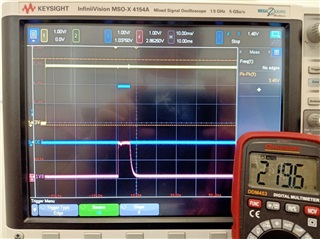

We have having 50% rejected rate due to high leakage current during off mode. The VCCA always supplied but VCCB is off during system sleep mode. And we can seen the high leakage current in our product. Can you advice any issue with this connection?

Best regards,

Felix