Other Parts Discussed in Thread: TIDA-01509

Dear Sir,

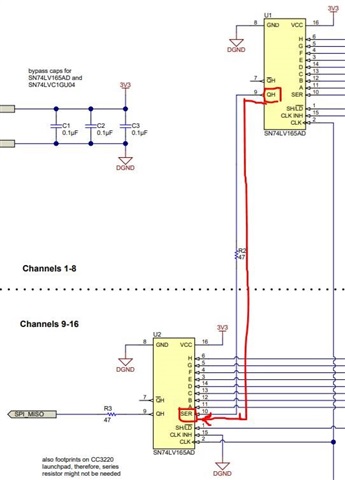

From TI reference design (TIDA-01509, https://www.ti.com/lit/pdf/tidrvh7), the U1 QH pin connect to U2 SER pin.

I am wondering to know what the layout length constraint is between one serial output QH to another register’s serial input SER.

Do we need to consider the propagation delay when layout design?