I was wondering what would happen with the subject device if VCCA is powered, EN is active (held low), translation DIR is from A-to-B, but VCCB is not powered.

Will there be any leakage current/voltage from VCCA rail to the VCCB rail?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

I was wondering what would happen with the subject device if VCCA is powered, EN is active (held low), translation DIR is from A-to-B, but VCCB is not powered.

Will there be any leakage current/voltage from VCCA rail to the VCCB rail?

Hey Michael,

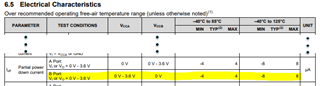

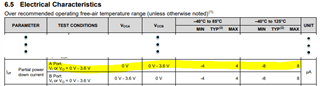

The partial power down leakage current, shown for when one of the rails is shut down, is listed in the datasheet.

Thanks!

Rami

Hey Michael,

After re-reading the question I believe I may have answered the wrong question here. Sorry about that!

Above I've listed the leakage of the I/O pins, which would be independent of the state of the OE pin since the Vcc isolation feature would already disable the I/O’s.

Now for what it looks like your actual question was.

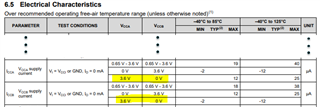

It looks like though what you may be actually asking about is the leakage of the supply pins VCCA and VCCB when VCCB is powered down and the /OE pin is held low. This is covered in the ICCA and ICCB specs in the datasheet:

You'll see that the input voltage, which includes the OE pin, is specified at either the VCCI (the VCC associated with the input port) or GND.

Sorry for the confusion and I hope this clears things up,

Rami Mooti

I am interested in the I/O leakage current while /OE signal is active, but VCCB=3.3V and powered, VCCA=1.8V but not powered, and the direction of translation is B -> A.

Hey Michael,

I'll revert you back to the first image then.

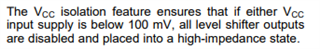

So Vcca is 0V in your condition, although it usually is 1.8V it's powered down so it's 0 for the time being. Under this condition the device will enter the Vcc isolation which effectively isolates the buses. From the datasheet :

Since this conditions already isolates the buses and puts them into a high-impedance state, the state of the /OE pin has no effect on the leakage through the I/O pins. The /OE pin when pulled high would just put the device in a high impedance state just the same When pulled low, it won't override the Vcc isolation. Note in the datasheet that the high-impedance state output current Ioz has the same specs as the partial power down current.

The parameters for this partial power off current when the VCC isolation condition is met (either supply below 100mV) is defined as Ioff in the datasheet (image above).

VCCB will be 3.3V which is encompassed in the 0-3.6V range specified.

So long as your I/O voltage remains between 0-3.6V you'll see at worst the leakage current listed under the temperature conditions specified above in the snippet from the datasheet.

Thanks,

Rami