Other Parts Discussed in Thread: CD74HC4046A

Hi team

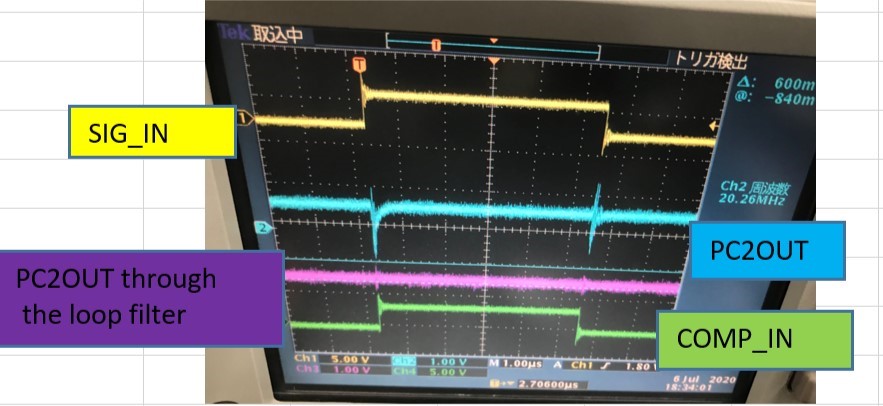

Now i use it as only phase comparator ( meaning i don't use its VCO).on my apprication, there is another Vcxo on the circit.Then,how will PCout act when i put the Ccxo clock.Then,how will PCout act when i put the same Vcxo clock to each of SIGin and Comp_in?

in other words,The Vcxo controlled by this IC and the Vcxo making the reference clock are in the same state, on my apprication.

Thank you very much.