Team,

my customer has a question regarding the timing requirement with VCC=3.3V.

Can you please give more details regarding:

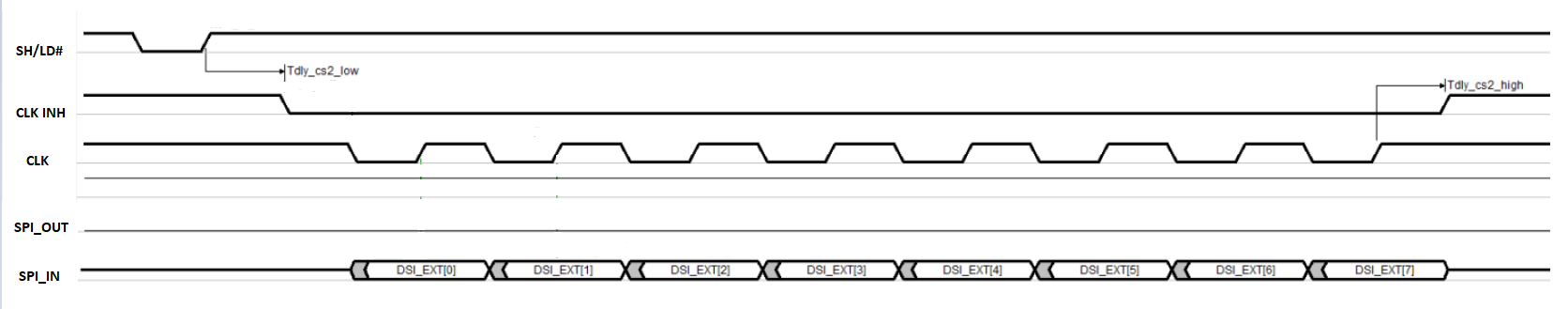

- The minimum CLK INH output delay from SH/LD# rising edge (Tdly_cs2_low)

- The minimum desabling delay of the CLK INH output following the last falling edge of the clock (Tdly_cs2_high)

Thanks and best regards