Hello there,

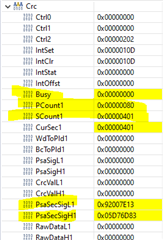

In my application, the DMA module RAM was hardware auto-initialized during system startup (MSIENA_bit.MSIENA1 = 1), and the DMA parity check has been enabled with DMAPCR_bit.PARITY_ENA=0xA.

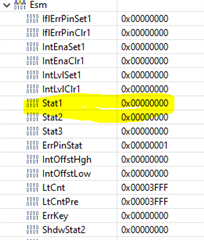

Following each DMA transfer for MibADC1 and MibSPI3, the ESM Group1 DMA parity error is declared (ESMSR1=0x00000008).

Following the CRC Engine Compression transfer, the ESM Group1 DMA parity error and DMA/DMM imprecise read error are declared (ESMSR1=0x00000028).

I've tried not activating the DMA RAM parity check, same behavior indicated by the ESMSR1 register.

Of course, this happens to more than one device.

Could you let me know where I should look at?

Thanks.