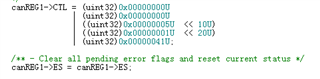

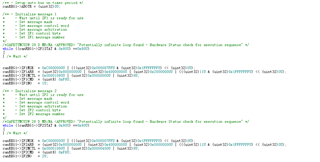

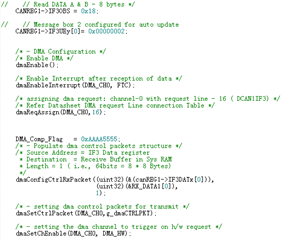

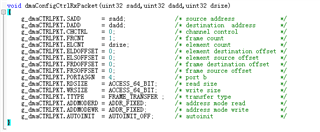

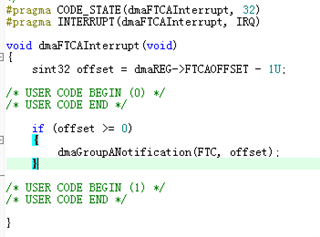

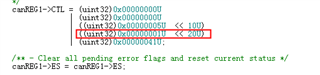

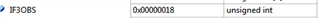

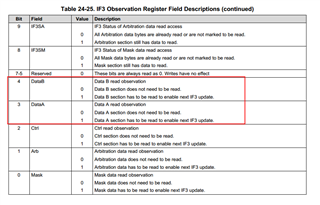

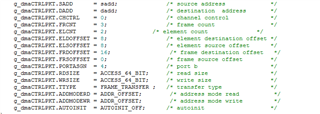

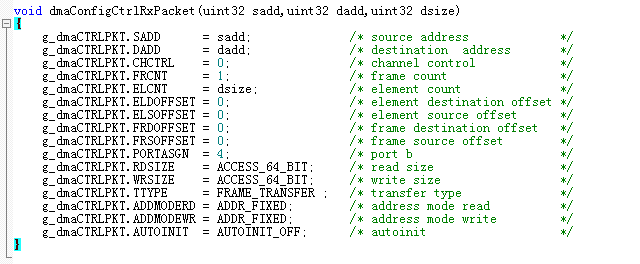

I want to use DMA mode to receive and send CAN data. I configured my program based on an example on the forum. When I sent data to the MCU, the interrupt only entered once, and there was no response when I sent it again. And I cannot configure the buffer size. When I increase the DMA buffer, I only receive one frame of data and enter the interrupt.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.