Hello team,

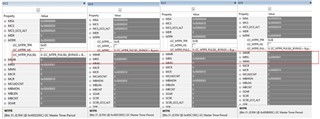

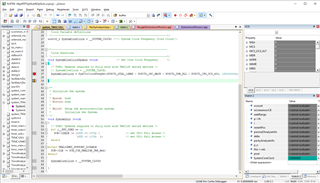

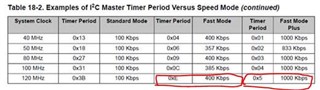

My customer uses the device with external 16MHz oscillator and 120MHz system clock.

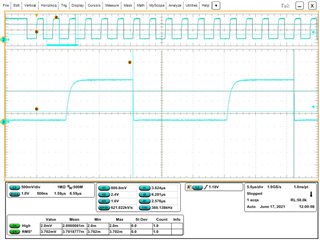

And customer uses both Fast Mode(400kbps) and Fast Mode Plus(1000kbps) I2C.

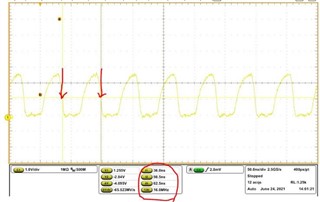

Customer measured clock frequency of the I2C signal, however what they observed is 387kHz for Fast mode and 922kHz for Fast mode plus.

Could you let me know typical(or target) SCL frequency for the conditions?

It would be helpful If its variation data is also available.

Best regards,