Part Number: TM4C123GH6PZ

A GPIO pin used within specified capabilities failed low / sinking current.

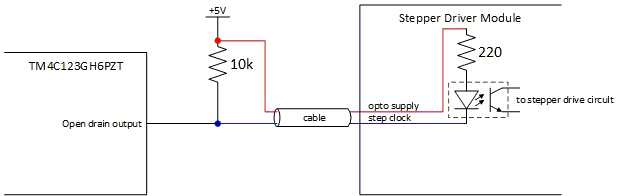

The pin is configured for PWM output with 8mA drive strength as required:

GPIOPinConfigure(GPIO_PH2_WT5CCP0);

GPIOPinTypeTimer(GPIO_PORTH_BASE, GPIO_PIN_2);

MAP_GPIOPadConfigSet(GPIO_PORTH_BASE, GPIO_PIN_2, GPIO_STRENGTH_8MA, GPIO_PIN_TYPE_OD);

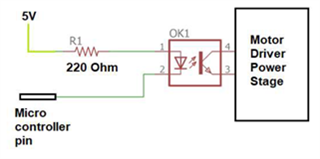

The pin is used as a low-side driver of an optocoupler on a separate PCB, circuit sketch below:

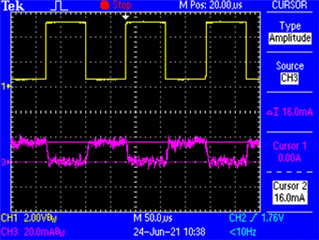

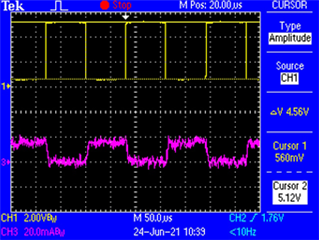

When the pin is driving the opto the following was measured on another (identical) copy of the board:

Vout: 0.56V

Iout: -16mA (into the pin)

The current measurement was confirmed under static conditions with a meter.

Scope screen captures:

Driving the opto is intermittent, but when on the switching frequency is between 1Hz and 30kHz. When idle the GPIO pin is pulled up to 5V.

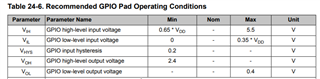

On one board the pin PH2 failed low, driving the opto. The current sink capability specified in table 24-6 of the data sheet states up to 18mA at Vo = 1.2V. We are well below that Vo level and below 18mA.