Hello,

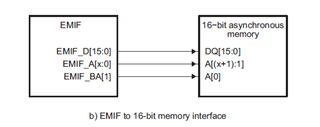

We are trying access a Async device via EMIF using nCS2 chip select of EMIF.

We are configuring EMIF to read 16 bit data.

When the pointer to the address is used using keyword UINT16, BA1 should be LSB of the address. Instead of that BA0 is getting configured as LSB.

Can you please let us know which datatype to be used to configure exactly for 16bit data.

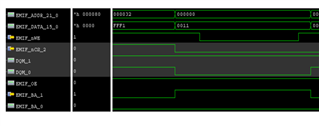

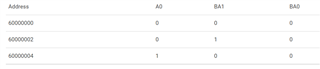

Below is the table of the outputs observed on A0,BA1&BA0 pins of J10 connector on the TMS570LC43x EVM.

| Address | A0 | BA1 | BA0 |

| 60000000 | 0 | 0 | 0 |

| 60000002 | 0 | 1 | 0 |

| 60000004 | 1 | 0 | 0 |

Also, attached snapshot of the code.