Part Number: TM4C1294KCPDT

Unknowingly been trying to get FPU to multiply two values ARM engineers seem to believe possible 7M4 FPU. Have single stepped CCS debug to discover horrific failure occurs, multiply 2 floating point values produce DEN. The exception occurs few instructions below the multiplication. The FPU is fully enabled and CPAC REG80 (CP10, CP11) have full access. The IP will not get past this issue cause Nmi exception. The value (theta) is being passes into the function prior to CPU IP vectoring into the void.

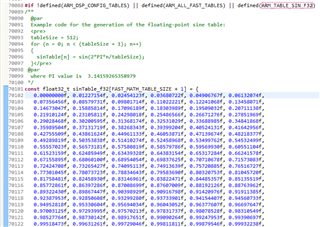

BTW: input theta = 0.0123450002 and how the 0002 gets added into float 32 bit array, e.g. theta[1]={0.0} value (0.012345) is a mystery.

Compiler TI v18.12.4.LTS, RunTimeSupport rtsv7M4_T_le_v4SPD16_eabi.lib, --float_support FPv4SDP16

Why is the 7M4 FPU not able to do single precision floating point multiplication, seems to be the question? I'm familiar with NAN acronym but what does DEN mean?